# FOR SYMMETRICAL GENERATION OF COMPLEMENTARY TTL SIGNALS

- Switching Time Skew of the Complementary Outputs is Typically 0.5 ns . . . Guaranteed to be No More than 3 ns at Rated Loading

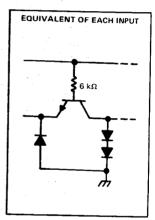

- Full Fan-Out to 20 High-Level and 10 Low-Level 54/74 Loads

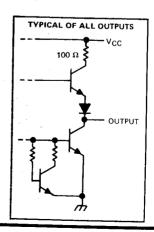

- Active Pull-Down Provides Square **Transfer Characteristic**

### description

The SN54265 and SN74265 circuits feature complementary outputs from each logic element, which have virtually symmetrical switching time delays from the triggering input. They are designed specifically for use in applications such as:

- Symmetrical clock/clock generators

- Complementary input circuit for decoders and code converters

- Switch debouncing

- Differential line driver

Examples of these four functions are illustrated in the typical application data.

The SN54265 is characterized for operation over the full military temperature range of -55°C to 125°C; the SN74265 is characterized for operation from 0°C to 70°C.

#### (TOP VIEW) U<sub>16</sub> V<sub>CC</sub> 1A 🛮 1 1W [ 2 15 T 4A **1Y** □3 14 \ 4W 2A 1 4 13 T4Y

SN54265 ... J OR W PACKAGE

SN74265 . . . J OR N PACKAGE

28∏5 12∏3B 2W∏6 11 T3A 2Y 🗆 7 10∏3W GND∏8 9∏3Y

NC - No internal connection

### schematics of inputs and outputs

## logic diagrams