### μPD8041AH, μPD8741A 8-BIT, SINGLE-CHIP NMOS MICROCOMPUTERS WITH UNIVERSAL PPI

### **Description**

The  $\mu$ PD8041AH and  $\mu$ PD8741A are programmable peripheral interface controllers intended for use in master/slave configurations with 8048, 8080A, 8085A, 8086, and other 8- and 16-bit microprocessors. The  $\mu$ PD8041AH/8741A functions as a totally self-sufficient controller with its own program and data memory to effectively unburden the master CPU from I/O handling and peripheral control functions.

The bus structure and data and status registers of the  $\mu$ PD8041AH/8741A allow easy interface to the master processor bus. This enables the processor to perform control tasks which offload main system processing and more efficiently distribute processing functions.

The  $\mu$ PD8041AH/8741A contains an 8-bit CPU, 1K $\times$ 8 program memory, 64 $\times$ 8 data memory, 18 I/O lines, a counter/timer, and a clock generator. The program memory for the  $\mu$ PD8041AH is factory mask-programmed, while program memory for the  $\mu$ PD8741A is UV EPROM for more flexibility.

#### **Features**

- □ Complete single chip microcomputer

- 8-bit CPU

- 1K × 8 ROM

- 64 × 8 RAM

- 8-bit timer/counter

- 18 I/O lines

- 8048-, 8080A-, 8085A-, 8086-compatible bus structure

- ☐ Asynchronous slave-to-master interface

- 8-bit status register

- Two data registers

- ☐ Interrupt, DMA, or polled operation

- □ Expandable I/O

- ☐ Single +5 V power supply

#### **Ordering Information**

| Part<br>Number | Package Type                     | Max Frequency<br>of Operation |

|----------------|----------------------------------|-------------------------------|

| µPD8041AHC     | 40-pin plastic DIP               | 11 MHz                        |

| μPD8741AD      | 40-pin cerdip with quartz window | 6 MHz                         |

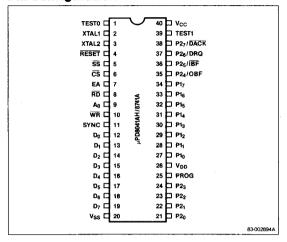

### **Pin Configuration**

### Pin Identification

| No.          | Symbol                           | Function                   |

|--------------|----------------------------------|----------------------------|

| 1            | TO                               | Testable input 0           |

| 2            | XTAL1                            | Crystal input 1            |

| 3            | XTAL2                            | Crystal input 2            |

| 4            | RESET                            | Reset input                |

| 5            | SS                               | Single step input          |

| 6            | <del>cs</del>                    | Chip select input          |

| 7            | EA                               | External access input      |

| 8            | RD                               | Read strobe input          |

| 9            | A <sub>0</sub>                   | Address input 0            |

| 10           | WR                               | Write strobe output        |

| 11           | SYNC                             | SYNC output                |

| 12-19        | D <sub>0</sub> -D <sub>7</sub>   | Bidirectional data bus     |

| 20           | V <sub>SS</sub>                  | Ground potential           |

| 21-24, 35-38 | P2 <sub>0</sub> -P2 <sub>7</sub> | Quasi-bidirectional Port 2 |

| 25           | PROG                             | Program pulse output       |

| 26           | V <sub>DD</sub>                  | Programming supply voltage |

| 27-34        | P1 <sub>0</sub> -P1 <sub>7</sub> | Quasi-bidirectional Port 1 |

| 39           | T1                               | Testable input 1           |

| 40           | V <sub>CC</sub>                  | Primary power supply       |

### Pin Functions

### XTAL1 (Crystal 1)

XTAL1 is one side of the crystal or external oscillator or external frequency source.

### XTAL2 (Crystal 2)

XTAL2 is the other side of the crystal or frequency source.

### T0 (Test 0)

To is the testable input using conditional transfer functions JTO, and JNTO. To can also be used during programming as a testable flag.

### T1 (Test 1)

T1 is the testable input using conditional transfer functions JT1 and JNT1. T1 can be made the counter/timer input using the STRT CNT instruction.

### **RESET** (Reset)

An active low on RESET initializes the processor. RESET is also used for PROM programming, verification, and power-down.

### SS (Single Step)

An active low on SS, together with the SYNC output, allows the processor to single step through each instruction in program memory.

### EA (External Access)

An active high on EA disables internal program memory and fetches and accesses external program memory.

#### RD (Read)

RD will pulse low when the processor reads data and status words from the data bus buffer or status register.

### WR (Write)

WR will pulse low when the processor writes data or status words to the data bus buffer or status register.

### D<sub>0</sub>-D<sub>7</sub> (Data Bus)

$D_0$ – $D_7$  is a three-state, bidirectional data bus.  $D_0$ – $D_7$  interfaces the  $\mu$ PD8041AH/8741A to the 8-bit master system's data bus.

### P10-P17 (Port 1)

P10-P17 is an 8-bit quasi-bidirectional port.

### P20-P27 (Port 2)

P20-P27 is an 8-bit quasi-bidirectional port. P20-P23 output the high-order four bits of the address during an external program memory fetch. P20-P23 also function as a 4-bit I/O bus for the  $\mu$ PD82C43 I/O port expander. P24-P27 can be used as port lines or interrupt requests (IBF and OBF) and DMA handshake signals (DRQ and DACK).

### PROG (Program Pulse)

PROG is used in programming the  $\mu$ PD8041AH/8741A. PROG is also used as an output pulse during a fetch when interfacing with the  $\mu$ PD82C43 I/O port expander.

### **V<sub>CC</sub>** (Primary Power Supply)

$V_{CC}$  is the primary power supply.  $V_{CC}$  must be  $+5\,V$  during programming and operation of the  $\mu PD8041AH$ .

### **VDD (Programming Supply Voltage)**

$V_{DD}$  is the programming supply voltage for programming the  $\mu PD8741AH$ . It is  $+5\,V$  for normal operation of the  $\mu PD8041AH/8741A$ .  $V_{DD}$  is also the low power standby input for the ROM version.

### Vss (Ground)

VSS is ground potential.

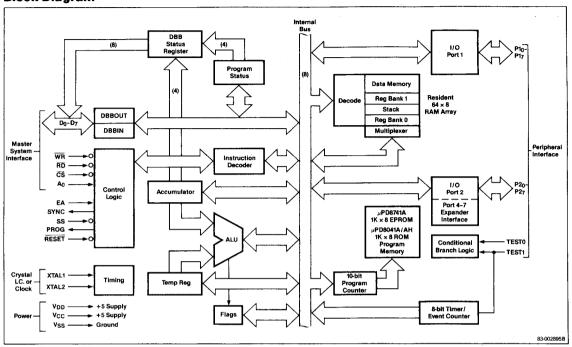

### **Block Diagram**

### **Absolute Maximum Ratings**

$T_{\Delta} = 25$  °C

| Power supply voltage, V <sub>CC</sub>   | -0.5 V to +7.0 V |

|-----------------------------------------|------------------|

| Power supply voltage, V <sub>DD</sub>   | -0.5 V to +7.0 V |

| Input voltage, V <sub>IN</sub>          | -0.5 V to +7.0 V |

| Output voltage, V <sub>0</sub>          | -0.5 V to +7.0 V |

| Operating temperature, T <sub>OPT</sub> | 0°C to +70°C     |

| Storage temperature, T <sub>STG</sub>   | -65°C to +150°C  |

Comment: Exposing the device to stresses above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational sections of the specification. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### Capacitance

$T_A = 25$ °C

|                       |                 |     | Limits |     |      | Test       |

|-----------------------|-----------------|-----|--------|-----|------|------------|

| Parameter             | Symbol          | Min | Тур    | Max | Unit | Conditions |

| Input<br>capacitance  | C <sub>1</sub>  |     |        | 10  | pF   |            |

| Output<br>capacitance | C <sub>IO</sub> |     |        | 20  | pF   |            |

## $\mu$ PD8041AH, $\mu$ PD8741A

**DC Characteristics**

$T_A = 0$ °C to +70°C,  $V_{CC} = V_{DD} = +5$  V ±10%;  $\mu$ PD8041AH:  $V_{DD} = +5$  V ±5%;  $\mu$ PD8741A:  $V_{SS} = 0$  V

|                        |                  |      | Lin             | nits  |                 |      |                                                                                                                   |

|------------------------|------------------|------|-----------------|-------|-----------------|------|-------------------------------------------------------------------------------------------------------------------|

|                        |                  | μPD8 | 741A            | µPD80 | 141AH           |      | Test                                                                                                              |

| Parameter              | Symbol           | Min  | Max             | Min   | Max             | Unit | Conditions                                                                                                        |

| Input voltage low      | VIL              | -0.5 | 0.8             | -0.5  | 0.8             | ٧    | All except X1, X2, and RESET                                                                                      |

| mpat ronage ion        | V <sub>IL1</sub> | -0.5 | 0.6             | - 0.5 | 0.6             | ٧    | X1, X2, RESET                                                                                                     |

| Input voltage high     | ViH              | 2.0  | V <sub>CC</sub> | 2.0   | V <sub>CC</sub> | V    | Except X1, X2, and RESET                                                                                          |

| mput rollago mg.       | V <sub>IH1</sub> | 3.8  | V <sub>CC</sub> | 3.8   | V <sub>CC</sub> | ٧    | X1, X2, RESET                                                                                                     |

| Output voltage low     | V <sub>OL</sub>  |      | 0.45            |       | 0.45            | ٧    | $D_0-D_7$ , SYNC, $I_{0i}=2.0 \text{ mA}$                                                                         |

| Catpat Totago is ii    | V <sub>OL1</sub> |      | 0.45            |       | 0.45            | ٧    | Except PROG, I <sub>OL</sub> = 1.0 mA                                                                             |

|                        | V <sub>OL2</sub> |      | 0.45            |       | 0.45            |      | PROG, $I_{OL} = 1.0 \text{ mA}$                                                                                   |

| Output voltage high    | V <sub>OH</sub>  | 2.4  |                 | 2.4   |                 | ٧    | $D_0 - D_7$ , $I_{OH} = -400 \mu\text{A}$                                                                         |

| output rollage mg.     | V <sub>OH1</sub> | 2.4  |                 | 2.4   |                 | V    | All other outputs:<br>$1_{OH} = -50 \mu A$                                                                        |

| Input current low      | lu               |      | 0.5             |       | 0.5             | mA   | P1 <sub>0</sub> -P1 <sub>7</sub> , P2 <sub>0</sub> -P2 <sub>7</sub> : V <sub>IL</sub> = 0.8 V                     |

| input current ion      | 1 <sub>L11</sub> | -    | 0.2             |       | 0.2             | mA   | $\overline{SS}$ , $\overline{RESET}$ ; $V_{IL} = 0.8 \text{ V}$                                                   |

| Input leakage current  | IIL              |      | ± 10            |       | ±10             | μΑ   | T0, T1, $\overline{RD}$ , $\overline{WR}$ , $\overline{CS}$ , EA, A <sub>0</sub> , $V_{SS} \le V_{IN} \le V_{CC}$ |

| Output leakage current | I <sub>OL</sub>  |      | ±10             |       | ±10             | μΑ   | $D_0$ - $D_7$ , High Z state,<br>$V_{SS}$ +0.45 V $\leq$ V <sub>IN</sub> $\leq$ V <sub>CC</sub>                   |

| Supply current (total) | IDD              |      | 15              |       | 15              | mA   | V <sub>DD</sub>                                                                                                   |

| cappi, sa. on (total)  | IDD+ICC          |      | 135             |       | 125             | mA   |                                                                                                                   |

### **AC Characteristics**

$T_A = 0$  °C to +70 °C,  $V_{CC} = V_{DD} = +5 \text{ V} \pm 10\% \text{ V}_{SS} = 0 \text{ V}$

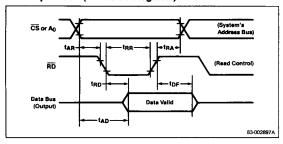

### DBB Read

|                                        |                 |               | Lin   | nits        |      |      |                                                                                         |

|----------------------------------------|-----------------|---------------|-------|-------------|------|------|-----------------------------------------------------------------------------------------|

|                                        |                 | μ <b>PD</b> 8 | 1741A | µPD80       | 41AH |      | Test                                                                                    |

| Parameter                              | Symbol          | Min           | Max   | Min         | Max  | Unit | Conditions                                                                              |

| CS, A <sub>0</sub> setup to RD ↓       | t <sub>AR</sub> | 300           |       | 0           |      | ns   |                                                                                         |

| CS, A <sub>0</sub> hold after RD ↑     | t <sub>RA</sub> | 30            |       | 0           |      | ns   |                                                                                         |

| RD pulse width                         | t <sub>RR</sub> | 300           |       | 160         |      | ns   |                                                                                         |

| CS, A <sub>0</sub> , to data out delay | t <sub>AD</sub> |               | 370   |             | 130  | ns   | $\mu$ PD8041A / 8741A: $C_L$ = 150 pF $\mu$ PD8041AH: $C_L$ = 100 pF                    |

| RD ↓ to data out delay                 | t <sub>RD</sub> |               | 200   | <del></del> | 130  | ns   | $\mu$ PD8041A / 8741A: $C_L = 150 \text{ pF}$<br>$\mu$ PD8041AH: $C_L = 100 \text{ pF}$ |

| RD † to data float delay               | t <sub>DF</sub> |               | 140   |             | 85   |      |                                                                                         |

| Cycle time                             | tcy             | 2.5           | 15    | 1.36        | 15   | ns   |                                                                                         |

AC Characteristics (cont)  $T_A=0\,^{\circ}\text{C to }+70\,^{\circ}\text{C}, \ V_{CC}=V_{DD}=+5\,\text{V}\pm10\%\ V_{SS}=0\,\text{V}$

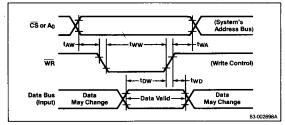

### **DBB Write**

|                                    |                 |               | Lin  | nits           |       |      |                                               |

|------------------------------------|-----------------|---------------|------|----------------|-------|------|-----------------------------------------------|

|                                    |                 | μ <b>PD</b> 8 | 741A | μ <b>PD8</b> ( | 041AH |      | Test                                          |

| Parameter                          | Symbol          | Min           | Max  | Min            | Max   | Unit | Conditions                                    |

| CS, A <sub>0</sub> setup to WR ↓   | t <sub>AW</sub> | Ö             |      | 0              |       | ns   |                                               |

| CS, A <sub>0</sub> hold after WR ↑ | t <sub>WA</sub> | 0             |      | 0              |       | ns   |                                               |

| WR pulse width                     | t <sub>WW</sub> | 250           |      | 160            |       | ns   | μPD8041A / 8741A:<br>t <sub>CY</sub> = 2.5 μs |

| Data setup to WR ↑                 | t <sub>DW</sub> | 150           |      | 130            |       | ns   |                                               |

| Data hold after WR ↑               | t <sub>WD</sub> | 0             |      | 0              |       | ns   |                                               |

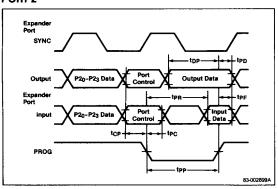

### Port 2

|                                |                 |               | Lin  | nits |       |      |                                        |

|--------------------------------|-----------------|---------------|------|------|-------|------|----------------------------------------|

|                                |                 | μ <b>PD</b> 8 | 741A | μPD8 | 041AH |      | Test                                   |

| Parameter                      | Symbol          | Min           | Max  | Min  | Max   | Unit | Conditions                             |

| Port control setup to PROG ↓   | t <sub>CP</sub> | 110           |      | 100  | e'    | ns   | μPD8041AH: C <sub>L</sub> = 80 pF      |

| Port control hold after PROG ↓ | t <sub>PC</sub> | 100           |      | 60   |       | ns   | $\mu$ PD8041AH: $C_L = 20 pF$          |

| Input data setup to PROG ↓     | t <sub>PR</sub> |               | 810  |      | 650   | ns   | μPD8041AH: C <sub>L</sub> = 80 pF      |

| Input data hold time           | tpF             | 0             | 150  | 0    | 150   | ns   | $\mu$ PD8041AH: C <sub>L</sub> = 20 pF |

| Output data setup time         | t <sub>DP</sub> | 250           |      | 200  |       | ns   | $\mu$ PD8041AH: C <sub>L</sub> = 80 pF |

| Output data hold time          | t <sub>PD</sub> | 65            |      | 65   |       | ns   | $\mu$ PD8041AH: C <sub>L</sub> = 20 pF |

| PROG pulse width               | tpp             | 1200          |      | 700  |       | ns   |                                        |

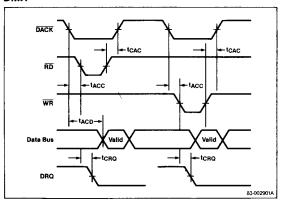

### DMA

|                                   |                  |      | Lin   | nits          |       |      |                                                |

|-----------------------------------|------------------|------|-------|---------------|-------|------|------------------------------------------------|

|                                   |                  | μPD8 | 3741A | μ <b>PD</b> 8 | 041AH |      | Test                                           |

| Parameter                         | Symbol           | Min  | Max   | Min           | Max   | Unit | Conditions                                     |

| DACK setup time to                | tACC             | 0    |       | 0             |       | ns   |                                                |

| DACK hold time after RD, WR       | †CAC             | 0    |       | 0             |       | ns   |                                                |

| Data output delay after DACK      | t <sub>ACD</sub> |      | 225   |               | 130   | ns   | $\mu$ PD8041A / 8741A: C <sub>L</sub> = 150 pF |

| DRQ clear delay time after RD, WR | t <sub>CRQ</sub> |      | 200   |               | 130   | ns   | μPD8041AH: C <sub>L</sub> = 100 pF             |

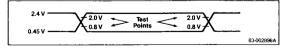

### **AC Timing Test Points**

### **Timing Waveforms**

### Read Operation (DBBOUT Register)

### Write Operation (DBBIN Register)

### PORT 2

#### DMA

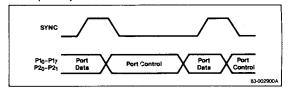

### PORT(EA = 1)

### **Functional Description**

Two data bus buffers, an 8-bit status register, the  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  inputs, and expandable I/O lines enhance the  $\mu\text{PD8041AH/8741A}$ . These features enable easier master/slave interface and increased functionality.

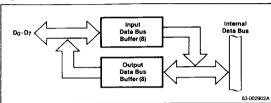

#### **Data Bus Buffers**

Figure 1 shows how the input and output data bus buffers enable a smooth data flow to and from the master processors.

Figure 1. Data Bus Buffers

### Status Register

The 8-bit status register includes four user-definable bits,  $ST_4-ST_7$ . Use the MOV STS, A instruction (90H) to define bits  $ST_4-ST_7$  by moving accumulator bits 4-7 to bits 4-7 of the status register. Bits  $ST_0-ST_3$  are not affected.

Figure 2 shows the format of the status register.

Figure 2. Status Register Format

| D <sub>7</sub>  | D <sub>6</sub>  | D <sub>5</sub>  | D <sub>4</sub>  | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> |

|-----------------|-----------------|-----------------|-----------------|----------------|----------------|----------------|----------------|

| ST <sub>7</sub> | ST <sub>6</sub> | ST <sub>5</sub> | ST <sub>4</sub> | F1             | F0             | IBF            | OBF            |

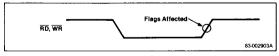

### RD and WR

The  $\overline{RD}$  and  $\overline{WR}$  inputs are edge-sensitive. Figure 3 shows that status bits  $\overline{IBF}$ , OBF, F1, and F0 are affected on the trailing edge at  $\overline{RD}$  or  $\overline{WR}$ .

Figure 3. RD and WR Inputs

### Port 24-Port 27

P24 and P25 can be used as either port lines or buffer status flag lines. This allows you to make OBF and  $\overline{\text{IBF}}$  status available externally to interrupt the master processor. Upon execution of the EN FLAGS instruction (F5H), P24 becomes the OBF pin. When a 1 is written to P24, the OBF pin is enabled and the status of OBF is output. A0 to P24 disables the OBF pin AND the pin remains low. This pin indicates valid data is available from the  $\mu$ PD8041AH/8741A.

An EN FLAGS instruction execution also enables P2 $_5$  to indicate that the  $\mu$ PD8041AH/8741A is ready to accept data. A $_1$  written to P2 $_5$  enables the  $\overline{IBF}$  pin and the status of  $\overline{IBF}$  is available on P2 $_5$ . A $_0$  written to P2 $_5$  disables the  $\overline{IBF}$  pin. If OBF is not true, the data at the data bus is invalid.

P26 and P27 can be used as either port lines or DMA handshake lines to allow DMA interface. The EN DMA instruction (E5H) enables P26 and P27 to be used as DRQ (DMA request) and DACK (DMA acknowledge), respectively.

When a 1 is written to P26, DRQ is activated and a DMA request is issued. The EN DMA instruction deactivates DRQ. You can also deactivate DRQ by adding DACK with RD or WR. Execution of the EN DMA instruction enables P27 (DACK) to function as a chip select input for the data bus buffer registers during DMA transfers.

| Instruction Set | on Set    |                                                                 |        |     | ٥              | Operation Code | Spool |        |                |                             |        |       | ļ |   |   | Flags | 1 1         |     |

|-----------------|-----------|-----------------------------------------------------------------|--------|-----|----------------|----------------|-------|--------|----------------|-----------------------------|--------|-------|---|---|---|-------|-------------|-----|

| Manage          | Operand   | Operation                                                       | 0,     | å   | ٥              | ď              | õ     | 20     | ā              | S<br>O                      | Cycles | Bytes | ပ | 2 | 2 | E .   | 08F ST4-ST7 | 31, |

| Accumulator     |           |                                                                 |        |     |                |                |       |        |                |                             |        |       | 1 |   | 1 |       |             |     |

| ACCUININGIO     | A. # data | (A) (A) + data                                                  | 0      | 0.  | ۰.             | 0 -            | 0 1   | 0,     |                | <del>-</del> - <del>-</del> | 2      | 2     | • |   |   |       |             |     |

|                 |           |                                                                 | 42     | 9   | 5              | 40             | g     | 5      | -              | 3                           |        |       |   |   |   |       |             |     |

| ADD             | A, Rr     | $(A) \leftarrow (A) + (Rr)$<br>r = 0-7                          | 0      | -   | -              | 0              | -     | _      | _              | _                           | _      | -     | • | ŀ | ļ |       |             |     |

| ADD             | A. @ Rr   | $(A) \leftarrow (A) + ((Rr))$<br>r = 0-1                        | 0      | -   | -              | 0              | 0     | 0      | 0              | _                           | -      | -     |   |   | 1 |       |             | 1   |

| ADDC            | A, # data | (A) ← (A) + (C) + data                                          | 9.0    | 0 8 | 0 %            | ~ ₽            | 0 &   | o 5°   | ~ <del>2</del> | d <sub>0</sub>              | 2      | 2     | • |   |   |       |             |     |

| ADDC            | A, Br     | (A) $\leftarrow$ (A) + (C) + (Rr)<br>r = 0-7                    | 0      | -   | -              | -              | -     | _      | _              | _                           | -      | -     | • |   |   |       |             | ł   |

| ADDC            | A, @ Rr   | (A) $\leftarrow$ (A) + (C) + ((Rr))<br>r = 0-1                  | 0      | -   | -              | -              | 0     | 0      |                | _                           | -      | -     | • |   |   |       |             | 1   |

| ANL             | A, # data | (A) ← (A) AND data                                              | 9      | - გ | ဝန             | - 4            | o &   | о<br>ф | - 5            | - 용                         | 2      | 2     |   | ŀ |   |       |             |     |

| ANL             | A, Rr     | (A) $\leftarrow$ (A) AND (Rr)<br>r = 0-7                        | 0      | -   | 0              | -              | -     | _      | _              | _                           | -      | -     |   |   |   |       |             |     |

| ANL             | A, @ Rr   | (A) $\leftarrow$ (A) AND ((Rr))<br>r = 0-1                      | 0      | -   | 0              | -              | 0     | 0      | 0              | _                           | -      | -     |   |   |   |       |             |     |

| ā               | A         | (A) ← NOT (A)                                                   | 0      | 0   | -              | -              | 0     | -      | -              | -                           | _      | -     |   |   |   |       |             |     |

| SI.B.           | · A       | (A) ← 0                                                         | 0      | 0   | -              | 0              | 0     | -      | -              | -                           | -      | -     |   |   | İ |       |             |     |

| DA              | A         |                                                                 | 0      |     | 0              | -              | 0     | -      | -              | -                           | -      | -     | • |   | Ì |       |             |     |

| SHO             | A         | (A) ← (A) – 1                                                   | 0      | 0   | 0              | 0              | 0     | -      | -              | -                           | -      | -     |   |   |   |       |             |     |

| INC             | A         | (A) ← (A) +1                                                    | 0      | 0   | 0              | -              | 0     | -      | -              | -                           | -      | -   • |   |   |   |       |             |     |

| ORL             | A, # data | (A) ← (A) OR data                                               | 0<br>4 | - გ | 0 <del>ද</del> | 0 p            | ဝဗ္   | 0 5°   | - 윤            | - 용                         | 2      | 2     |   |   |   |       |             |     |

| ORL             | A, Br     | (A) (A) OR (Br)<br>r = 0-7                                      | 0      | -   | 0              | 0              | -     | _      | -              | -                           | -      | -     |   |   |   |       |             |     |

| ORL             | A, @ Rr   | (A) ← (A) OR ((Rr))<br>r = 0−1                                  | 0      | -   | 0              | 0              | 0     | 0      | 0              | _                           | -      | -     |   | ļ |   |       |             |     |

| H.              | A         | $(AN + 1) \leftarrow (AN); N = 0-6$<br>$(A_0) \leftarrow (A_7)$ | -      | _   | -              | 0              | 0     | -      | -              | -                           | -      | -     |   |   |   |       |             | ļ   |

|                 |           |                                                                 |        |     |                |                |       |        |                |                             |        |       |   |   |   |       |             |     |

4-300

| Instruction Set    | ion Set (cont) |                                                                                          |     |                |                |                                       |                  |     |               |                                                                 |       |   |   |   |       |          |         |     |

|--------------------|----------------|------------------------------------------------------------------------------------------|-----|----------------|----------------|---------------------------------------|------------------|-----|---------------|-----------------------------------------------------------------|-------|---|---|---|-------|----------|---------|-----|

|                    |                |                                                                                          |     |                | ြီ             | Operation Code                        | S<br>S<br>S<br>S |     |               |                                                                 |       |   |   |   | Flags | _        |         |     |

| Mnemonic           | Operand        | Operation                                                                                | 5   | ے              | D <sub>S</sub> | 2                                     | ء<br>م           | 2   | 2             | D7 D6 D6 D4 D3 D2 D1 D0 Cycles Bytes C AC F0 F1 IBF OBF ST4-ST7 | Bytes | ပ | ¥ | 2 | E     | <b>8</b> | IF ST4- | ST, |

| Accumulator (cont) | cont)          |                                                                                          |     |                |                |                                       |                  |     |               |                                                                 |       |   |   |   |       |          |         |     |

| RLC                | Ą              | $(AN + 1) \leftarrow (AN)$ ; N = 0-6<br>$(A_0) \leftarrow (C)$<br>$(C) \leftarrow (A_7)$ | -   | -              | -              | 1 1 1 0 1 1 1                         | 0                | _   | _             | -                                                               | -     | • |   |   |       |          |         |     |

| 88                 | A              | $(AN) \leftarrow (AN + 1); N = 0-6$<br>$(A_7) \leftarrow (A_0)$                          | 0   | -              | -              | 0 1 1 0 1 1                           | 0                |     | -             | -                                                               | -     |   |   |   |       |          |         |     |

| RRC                | A              | $(AN) \leftarrow (AN + 1); N = 0-6$<br>$(A_7) \leftarrow (C)$<br>$(C) \leftarrow (A_0)$  | 0   | -              |                | 0 0 1                                 | 0                | _   | _             | -                                                               | -     | • |   |   |       |          |         |     |

| SWAP               | Ą              | (A <sub>4</sub> -A <sub>7</sub> ) ← (A <sub>0</sub> -A <sub>3</sub> )                    | 0   | -              | 0              | 0 0                                   | 0                |     | -             | -                                                               | -     |   |   |   |       |          |         |     |

| XRL                | A, # data      | (A) ← (A) XOR data                                                                       | - ¢ | - <del>8</del> | ၀ န            | 1 1 0 1 0 0 1<br>d7 d6 d5 d4 d3 d2 d1 | 9                | 2 d | - 8           | 2                                                               | 2     |   |   |   |       |          |         |     |

| XRL                | A, Br          | (A) $\leftarrow$ (A) XOR (Rr)<br>r = 0-7                                                 | -   | -              | 0              | -                                     | -                | _   | _             | -                                                               | -     |   |   |   |       |          |         |     |

| XBL                | A, @ Rr        | (A) $\leftarrow$ (A) XOR ((Rr))<br>r = 0-1                                               | -   | -              | 0              | -                                     | 0                |     | 1 0 1 0 0 0 1 | -                                                               | -     |   |   |   |       |          |         |     |

| Instructio      | Instruction Set (cont) |                                                                      |                 |            | ا              | Oneration Code | 900        |                               |                               |        |       |   |    |   | Flags |     |         |

|-----------------|------------------------|----------------------------------------------------------------------|-----------------|------------|----------------|----------------|------------|-------------------------------|-------------------------------|--------|-------|---|----|---|-------|-----|---------|

| Mnemonic        | Operand                | Operation                                                            | 6               | å          | å              | ď              |            | D <sub>2</sub>                | õ                             | Cycles | Bytes | ပ | 9¢ | 5 | 186   | OBF | 514-517 |

| Branch          |                        |                                                                      |                 |            |                |                |            |                               |                               |        |       |   |    |   |       |     |         |

| 71117           | Dr. addr               | (Rr) ← (Rr) – 1: r = 0-7                                             | -               | -          |                | 0              | _          | _                             | _                             | 2      | 2     |   |    |   |       |     |         |

| DUNZ            | , add                  | If (Rr) ≠ 0;                                                         | a <sub>7</sub>  | ુક<br>જ    | <b>9</b> 2     | æ<br>Æ         | 83<br>8    | a <sub>2</sub> a <sub>1</sub> | -<br>9                        |        |       |   |    |   |       |     |         |

|                 |                        | (PC0-PC7) addl                                                       |                 |            |                |                |            |                               | 6                             | 6      | ,     |   |    |   |       |     |         |

| JB <sub>b</sub> | addr                   | $(PC_0 - PC_7) \leftarrow addr \text{ if } B_b = 1$                  | 2 t             | <u> </u>   | ු ද            |                | - e        | - %<br>- %                    | > Æ                           | 7      | 7     |   |    |   |       |     |         |

|                 |                        | $(PC) \leftarrow (PC) + 2    Bb = 0$                                 | 3               | 3          | ۶ .            | 1              |            | 1                             | İ                             | 6      | ,     |   |    |   |       |     |         |

| 2               | addr                   | $(PC_0-PC_7) \leftarrow addr$ if $C = 1$                             |                 | - ,        | - ,            |                | ,<br>0     | - 8                           | ⊃ å                           | 7      | 7     |   |    |   |       |     |         |

|                 |                        | $(PC) \leftarrow (PC) + 2 \text{ if } C = 0$                         | 97              | .g         | જુ             | ਰ              | - [        | ١                             |                               |        | 6     |   |    |   |       |     |         |

| FO              | addr                   | $(PC_0-PC_7)$ addr if $F0 = 1$                                       | -               | 0          | -              |                | o .        |                               |                               | 2      | 7     |   |    |   |       |     |         |

| ,<br>5          |                        | $(PC) \leftarrow (PC) + 2 \text{ if } F0 = 0$                        | <b>a</b> 7      | ge<br>ge   | ફુ             | 25             | l          | a <sub>2</sub> a <sub>1</sub> | -                             |        |       |   |    |   |       |     |         |

| ū               | addr                   | (PCo-PC2) ← addr if F1 = 1                                           | 0               | -          |                | <b>-</b>       |            |                               | -                             | 7      | 2     |   |    |   |       |     |         |

| -               |                        | $(PC) \leftarrow (PC) + 2 \text{ if } F1 = 0$                        | <b>a</b> 7      | 8          | a5             | 94             | a3 ;       | a <sub>2</sub> a <sub>1</sub> |                               |        |       |   |    |   |       |     |         |

| 940             | oddr                   | (PCo-PC10) - (addra-addr10)                                          | a <sub>f0</sub> | gg.        | 38             | 0              | 0          | -                             |                               | 2      | 2     |   |    |   |       |     |         |

| r<br>F          | מחח                    | (PCn−PC <sub>7</sub> ) ← (addrn−addr <sub>7</sub> )                  | a <sub>7</sub>  | , %        | સુ             | a4             | 83         | a <sub>2</sub> a <sub>1</sub> | -1<br>90                      |        |       |   |    |   |       |     |         |

|                 |                        | (PC <sub>11</sub> ) ← 0BF                                            |                 |            |                |                |            |                               |                               |        |       |   |    |   |       |     |         |

| ddWi            | Ø.A                    | (PC <sub>0</sub> -PC <sub>7</sub> ) ← ((A))                          | -               | 0          | -              | -              | 0          | 0                             | -                             | 2      | -     |   |    |   |       |     |         |

| 0               | : - S                  | $(PC_{-}PC_{-}) \leftarrow addr if C = 0$                            | -               | -          | -              | 0              | 0          | _                             | 0                             | 2      | 2     |   |    |   |       |     |         |

| JNC             | and                    | $(PC) \leftarrow (PC) + 2 \text{ if } C = 1$                         | 97              | မွ         | a <sub>5</sub> | <b>9</b> 4     |            | a <sub>2</sub> a              | al a                          |        |       |   | :  |   |       |     |         |

| , direct        | 7000                   | (PCPC) addr if IBF = 0                                               | -               | -          | 0              | -              | 0          |                               | 1 0                           | 2      | 2     |   |    |   |       |     |         |

| Jainic          | anni                   | $(PC) \leftarrow (PC) + 2 \text{ if } 1BF = 1$                       | a <sub>7</sub>  | 9e         | <b>.</b> 85    | a4             | કુ         | a <sub>2</sub>                | a <sub>1</sub> a <sub>0</sub> |        |       |   |    |   |       |     |         |

| 100             |                        | (PCo-PC+) addr if 08F = 1                                            | -               | 0          | 0              | 0              | 0          | -                             | 1                             | 2      | 2     |   |    |   |       |     |         |

| ranc            |                        | $(PC) \leftarrow (PC) + 2 \text{ if } 0BF = 0$                       | a <sub>7</sub>  | æ          | a5             | <b>3</b> 4     | <b>9</b> 3 | a <sub>2</sub>                | a <sub>1</sub> a              |        |       |   |    |   |       |     |         |

| OLIVI           | oddr                   | (PC <sub>n</sub> -PC <sub>2</sub> ) 4- addr if T0 = 0                | 0               | 0          | -              | 0              | 0          |                               | 1                             | 2      | 7     |   |    |   |       |     |         |

| OIND            | 500                    | (PC) - (PC) + 2 if T0 = 1                                            | a <sub>7</sub>  | <b>9</b> 6 | 95             | 94             | a3         | 28                            | g 9                           |        |       |   |    |   |       |     |         |

| INI             | addr                   | (PC <sub>0</sub> -PC <sub>7</sub> ) ← addr if T1 = 0                 | 0               | -          | 0              | 0              | 0          |                               | 0                             | 2      | 2     |   |    |   |       |     |         |

|                 |                        | $(PC) \leftarrow (PC) + 2 \text{ if } T1 = 1$                        | 42              | ક્ષ        | a <sub>5</sub> | g4             | g,         | g5                            | . a                           |        | ,     |   |    |   |       |     |         |

| JNZ             | addr                   | $(PC_0-PC_7)$ addr if A = 0                                          | - 4             | 0 %        | ،<br>د         | - 3            | 0 %        | ج                             | - 4<br>- 6                    | ~ <    | 7     |   |    |   |       |     |         |

|                 |                        | (PC) +- (PC) + 2    A = 1                                            | 9/              | 8          | ક              | 4              | 3          | Ì                             |                               | 0      | 6     |   |    |   |       |     |         |

| FL              | addr                   | $(PC_0-PC_7) \leftarrow addr \ if \ if \ if \ if \ if \ if \ if \ i$ | g 6             | > ફ        | > %            | - 45           | - &        | - Z                           | а<br>В<br>В                   |        | ı     |   |    |   |       |     |         |

|                 |                        | (pCDC_) addr if T() = 1                                              | 0               | 0          | -              | -              | 0          | -                             | 1                             | 2      | 2     |   |    |   |       |     |         |

| 010             | 900                    | $(PC) \leftarrow (PC) + 2 \text{ if } T0 = 0$                        | a <sub>7</sub>  | a6         | a <sub>5</sub> | <b>3</b> 4     | gg<br>33   | a <sub>2</sub>                | a <sub>1</sub> a              | 0      |       |   |    |   |       |     |         |

| E               | addr                   | (PCo-PCz) ← addr if T1 = 1                                           | 0               | -          | 0              | -              | 0          | l                             |                               | 0 2    | 5     |   |    |   |       |     |         |

| _               | 5                      | $(PC) \leftarrow (PC) + 2 \text{ if } T1 = 0$                        | a7              | ge<br>9e   | a <sub>5</sub> | 34             | 83         | <b>a</b> 2                    | a a                           | ١      |       |   |    |   |       |     |         |

| Zſ              | addr                   | $(PC_0-PC_7) \leftarrow addr \text{ if } A = 0$                      | - 8             | ا          | 0 %            | 0 ;            | 0 %        | - 4                           | - 4                           | 2 2    | 5     |   |    |   |       |     |         |

|                 |                        | (PC) ← (PC) + 2 II A = 1                                             | 47              | ę          | ę              | 2              | 3          | 1                             | 1                             |        |       |   |    |   |       |     |         |

4-302

# NEC

|            |                                      |                                                                                            |      | i   | 0    | Operation Code | n Code         |                       |                |                       |         | ĺ  |   | 1 | = | Flags |     |         |

|------------|--------------------------------------|--------------------------------------------------------------------------------------------|------|-----|------|----------------|----------------|-----------------------|----------------|-----------------------|---------|----|---|---|---|-------|-----|---------|

| Mnemonic   | Operand                              | Operation                                                                                  | 0    | ے   | Š    | ď              | ũ              | 02                    | -              | D <sub>0</sub> Cycles | s Bytes | ပြ | Ş | 윤 | ᇤ |       | OB. | ST4-ST7 |

| Control    |                                      |                                                                                            |      |     |      |                |                |                       |                |                       |         |    |   |   |   | İ     |     |         |

| ENI        | Enable the external interrupt input  |                                                                                            | 0    | 0   | 0    | 0              | 0              | •                     | 0              | -                     | -       |    |   |   |   |       |     |         |

| DIS 1      | Disable the external interrupt input |                                                                                            | 0    | 0   | 0    | -              | 0              | -                     | 0              | -                     | -       |    |   |   |   |       |     |         |

| SEL RB0    | (BS) ← 0                             |                                                                                            | -    | -   | 0    | 0              | 0              | -                     | 0              | -                     | -       |    |   |   |   |       |     |         |

| SEL RB     | (BS) ← 1                             |                                                                                            | -    | -   | 0    | -              | 0              | -                     | 0              | -                     | -       |    |   |   |   |       |     |         |

| EN DMA     | Enable DMA handshake                 | ake                                                                                        | -    | -   | -    | -              | 0              | -                     | 0              | -                     | -       |    |   |   |   |       |     |         |

| EN FLAGS   | Enable interrupt to master device    | aster                                                                                      | -    | -   | -    | 0              | 0              | -                     | 0              | -                     | -       |    |   |   |   |       |     |         |

| Data Moves |                                      |                                                                                            |      |     |      |                |                |                       |                |                       |         |    |   |   |   |       |     |         |

| MOV        | A, # data                            | (A) ← data                                                                                 | 0 \$ | ဝန္ | - 45 | o \$           | 0 £            | -<br>-<br>-<br>-<br>- | - 2            | 1<br>do 2             | 2       |    |   |   |   |       |     |         |

| MOV        | A, Rr                                | (A) ← (Rr); r = 0-7                                                                        | -    | -   | -    | -              | -              | L                     | _              | -                     | -       |    |   |   |   |       |     |         |

| MOV        | A, @ Rr                              | (A) $\leftarrow$ ((Rr)); r = 0-1                                                           | -    | -   | -    | -              | 0              | 0                     | 0              | r 1                   | 1       |    |   |   |   |       |     |         |

| MOV        | A, PSW                               | (A) ← (PSW)                                                                                | -    | -   | 0    | 0              | 0              | -                     | _              | -                     | -       |    |   |   |   |       |     |         |

| MOV        | Rr, # data                           | (Rr) data; r = 0-7                                                                         | t 6  | 0 8 | - 운  | - 4            | <del>-</del> इ | r<br>d2               | - <del>P</del> | r 2<br>do             | 2       |    |   |   |   |       |     |         |

| MOV        | Rr, A                                | (Rr) ← (A); r = 0-7                                                                        | -    | 0   | -    | 0              | -              | _                     | _              |                       | -       |    |   |   |   |       |     |         |

| MOV        | @ Rr, A                              | $((Rr)) \leftarrow (A); r = 0-1$                                                           | -    | 0   | -    | 0              | 0              | 0                     |                | -                     | -       |    |   |   |   |       |     |         |

| MOV        | @ Rr, # data                         | ((Rr)) ← data; r = 0-1                                                                     | - 6  | 0 8 | - 왕  | - \$           | ဝန္            | o 5                   | 0<br>G         | r 2<br>do             | 2       |    |   |   |   |       |     |         |

| MOV        | PSW, A                               | (PSW) ← (A)                                                                                | -    | -   | 0    | -              | 0              | -                     | _              | 1 1                   | 1       |    |   |   |   |       |     |         |

| MOVP       | A, @ A                               | $(PC_0-PC_7) \leftarrow (A)$ $(A) \leftarrow ((PC))$                                       | -    | 0   | -    | 0              | 0              | 0                     | -              | 1 2                   | -       |    |   |   |   |       |     |         |

| MOVP3      | A, @ A                               | $(PC_0-PC_7) \leftarrow (A)$<br>$(PC_8-PC_{10}) \leftarrow 011$<br>$(A) \leftarrow ((PC))$ | -    | -   | -    | 0              | 0              | 0                     | -              | 1 2                   | -       |    |   |   |   |       |     |         |

| XCH        | A, Rr                                | (A) ↔ (Rr); r = 0-7                                                                        | 0    | 0   | -    | 0              | -              | _                     | _              | r 1                   | -       |    |   |   |   |       |     |         |

| ХСН        | A, @ Rr                              | (A) $\leftrightarrow$ ((Rr)); $r = 0-1$                                                    | 0    | 0   | -    | 0              | 0              | 0                     | 0              | r 1                   | 1       |    |   |   |   |       |     |         |

| хсно       | A, @ Rr                              | $(A_0-A_3) \leftrightarrow ((Rr))_0-((Rr))_3;$                                             | 0    | 0   | -    | -              | 0              | 0                     | 0              | -                     | -       |    |   |   |   |       |     |         |

Instruction Set (cont)

|                |            |                                                                          |         |       | ۱      | Operation Code | Code    |                     |       | :              |        |       |   |   |   | Flace |     |   |         |

|----------------|------------|--------------------------------------------------------------------------|---------|-------|--------|----------------|---------|---------------------|-------|----------------|--------|-------|---|---|---|-------|-----|---|---------|

|                |            |                                                                          | •       |       | 1      |                |         |                     | -1    |                |        |       | , | 1 | 4 | 3 I   | l.  | - | 3       |

| MINEMONIC      | Operand    | Operation                                                                | 5       | 5     | 2      | 3              | ន       | 2                   | 5     | S              | Cycles | By188 | د | 2 |   | ַ     | - 1 |   | 214-217 |

| riags          |            |                                                                          |         |       |        |                |         |                     |       |                |        |       |   |   |   |       |     |   |         |

| CPLC           |            | $(C) \leftarrow NOT(C)$                                                  | -       | 0     | -      | 0              | 0       | -                   | -     | -              | _      | -     | • |   |   |       |     |   |         |

| CPL F0         |            | (F0) ← NOT (F0)                                                          | +       | 0     | 0      | -              | 0       | -                   | 0     | 1              | 1      | -     |   |   | • |       |     |   |         |

| CPL F1         |            | (F1) NOT (F1)                                                            | -       | 0     | -      | -              | 0       | -                   | 0     | -              | -      | -     |   |   |   |       |     |   |         |

| CLRC           |            | 0 <del> (</del> 2)                                                       | -       | 0     | 0      | -              | 0       | -                   | -     | _              | -      | -     | • |   |   |       |     |   |         |

| CLR F0         |            | (F0) ← 0                                                                 | -       | 0     | 0      | 0              | 0       | -                   | 0     | -              | _      | _     |   |   |   |       |     |   |         |

| CLRF1          |            | (F1) ← 0                                                                 | -       | 0     | -      | 0              | 0       | -                   | 0     | -              | -      | -     |   |   |   |       |     |   |         |

| MOV STS, A     |            | ST4-ST7 A4-A7                                                            | -       | 0     | 0      | -              | 0       | 0                   | 0     | 0              | _      | -     |   |   |   |       |     |   |         |

| Input / Output |            |                                                                          |         |       |        |                |         |                     |       |                |        |       |   |   |   |       |     |   |         |

| ANL            | Pp, # data | (Pp) $\leftarrow$ (Pp) AND data<br>p = 1-2                               | - 6     | ဝန္   | 0 %    | - 4            | - చ్    | o &                 | σ£    | <del>-</del> گ | 2      | 2     |   |   |   |       |     |   |         |

| ANLD           | Pp, A      | (Pp) $\leftarrow$ (Pp) AND (A <sub>0</sub> -A <sub>3</sub> );<br>p = 4-7 | -       | 0     | 0      | -              | -       | -                   | ۵     | <u> </u>       | 2      | -     |   |   |   |       |     |   |         |

| 2              | A, Pp      | (A) $\leftarrow$ (Pp); p = 1-2                                           | 0       | 0     | 0      | 0              | -       | 0                   | a     | ۵              | 2      | -     |   |   |   |       |     |   |         |

| 2              | A, DBB     | (A) (DBB)                                                                | 0       | 0     | -      | 0              | 0       | 0                   | -     | 0              | -      | -     |   |   |   |       |     |   |         |

| MOVD           | A, Pp      | $(A_0-A_3) \leftarrow (Pp); p = 4-7$<br>$(A_4-A_7) \leftarrow 0$         | 0       | 0     | 0      | 0              | -       | -                   | ۵     | a              | 2      | -     |   |   |   |       |     |   |         |

| MOVD           | Pp, A      | $(Pp) \leftarrow (A_0 - A_3); p = 4-7$                                   | 0       | 0     | -      | -              | -       | -                   | ۵     | ۵              | _      | -     |   |   |   |       |     |   |         |

| ORLD           | Pp, A      | (Pp) $\leftarrow$ (Pp) OR (A <sub>0</sub> -A <sub>3</sub> );<br>p = 4-7  | -       | 0     | 0      | 0              | -       | -                   | ۵     | a.             | -      | -     |   |   |   |       |     |   |         |

| ORL            | Pp, # data | (Pp) ← (Pp) OR data<br>p = 1-2                                           | 1<br>d7 | ဝန္   | o<br>& | 0<br>d4        | դ<br>գ₃ | 0<br>d <sub>2</sub> | d,    | р<br>ф         | 2      | 2     |   |   |   |       |     |   |         |

| 00T            | DBB, A     | (DBB) ← (A)                                                              | 0       | 0     | 0      | 0              | 0       | 0                   | 1     | 0              | +      | 1     |   |   |   |       | -   |   |         |

| OUTL           | Pp, A      | $(Pp) \leftarrow (A); p = 1-2$                                           | 0       | 0     | -      | -              | -       | 0                   | d     | a              | _      | -     |   |   |   |       |     |   |         |

| negisters      | (-0) -0    | 10 - 10 - 10 - 10 - 10 - 10 - 10 - 10 -                                  | ,       | -     | 6      | 6              | -       |                     |       |                |        |       |   |   |   |       |     |   |         |

| No.            | (In) In    | $(RI) \leftarrow (RI) = 1, I = 0^{-1}$                                   | -   -   | -   - | - c    | -              |         | -   .               | _   . | _   .          | -   -  | -   - |   |   |   |       |     |   |         |

| INC            | @ Rr       | ((Rr)) ← ((Rr)) + 1;<br>r = 0-1                                          | 0       | 0     | 0      |                | - 0     | . 0                 | . 0   |                | .   -  |       |   |   |   |       |     |   |         |

|                |            |                                                                          |         |       |        |                |         |                     |       |                |        |       |   |   |   |       |     |   |         |

|                 |                                                                  |                                                                                                                                                                                                                                                                  |                 |          | ŏ        | <b>Operation Code</b> | <b>9</b><br>00 |                               |                |        |       |   |    |   | Flags |       |           |

|-----------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------|----------|-----------------------|----------------|-------------------------------|----------------|--------|-------|---|----|---|-------|-------|-----------|

| Mnemonic        | Operand                                                          | Operation                                                                                                                                                                                                                                                        | D,              | ď        | Dş       | D4                    | 0              | D <sub>2</sub> D <sub>1</sub> | 0              | Cycles | Bytes | ပ | ¥C | 6 | 표     | F 08F | F ST4-ST7 |

| Subroutine      |                                                                  |                                                                                                                                                                                                                                                                  |                 |          |          |                       |                |                               |                |        |       |   |    |   |       |       |           |

| CALL            | addr                                                             | ((SP)) ← (PC),<br>(PSW <sub>4</sub> -PSW <sub>7</sub> ),<br>(SP) ← (SP) + 1<br>(PC <sub>9</sub> -PC <sub>10</sub> ) ← (addig-addr <sub>10</sub> )<br>(PC <sub>9</sub> -PC <sub>7</sub> ) ← (addr <sub>0</sub> -addr <sub>7</sub> )<br>(PC <sub>11</sub> ) ← DB ← | a <sub>10</sub> | 8 8<br>8 | 8 8<br>5 | - 4g                  | 33<br>33<br>3  | 42 ay                         | 94<br>90<br>90 | ~      | ~     |   |    |   |       |       |           |

| RET             |                                                                  | $\begin{array}{c} \text{(SP)} \leftarrow \text{(SP)} = 1 \\ \text{(PC)} \leftarrow \text{((SP))} \end{array}$                                                                                                                                                    | -               | 0        | 0        | 0                     | 0              | 0                             | _              | 2      | -     |   |    |   |       |       |           |

| RETR            |                                                                  | $ (SP) \leftarrow (SP) = 1 $ $ (PC) \leftarrow ((SP)) $ $ (PSW_4 - PSW_7) \leftarrow ((SP)) $                                                                                                                                                                    | -               | 0        | 0        | -                     | 0              | 0                             | _              | 2      | -     |   |    |   |       |       |           |

| Timer / Counter |                                                                  |                                                                                                                                                                                                                                                                  |                 |          |          |                       |                |                               |                |        |       |   |    |   |       |       |           |

| EN TCNTI        | Enable internal interrupt<br>flag for timer / counter<br>output. |                                                                                                                                                                                                                                                                  | 0               | 0        | -        | 0                     | 0              | 1 0                           | _              | -      | -     |   |    |   |       |       |           |

| DIS TCNTI       | Disable internal interrupt flag for timer / counter output.      |                                                                                                                                                                                                                                                                  | 0               | 0        | -        | -                     | 0              | 0                             |                | -      | -     |   |    |   |       |       |           |

| M0V A, T        | (A) ← (T)                                                        |                                                                                                                                                                                                                                                                  | 0               | -        | 0        | 0                     | 0              | -                             | 0              | -      | -     |   |    |   |       |       |           |

| MOV T, A        | (T) <del>(</del> A)                                              |                                                                                                                                                                                                                                                                  | 0               | -        | -        | 0                     | 0              | 0                             | 0              | -      | -     |   |    |   |       |       |           |

| STOP TCNT       | Stop count for event counter.                                    |                                                                                                                                                                                                                                                                  | 0               | -        | -        | 0                     | 0              | 1 0                           | _              | -      | -     |   |    |   |       |       |           |

| STRT CNT        | Start count for event counter.                                   |                                                                                                                                                                                                                                                                  | 0               | -        | 0        | 0                     | 0              | 1 0                           | _              | -      | -     |   |    |   |       |       |           |

| STRT T          | Start count for timer.                                           |                                                                                                                                                                                                                                                                  | 0               | -        | 0        | -                     | 0              | 10                            | 1              | -      | -     |   |    |   |       |       |           |

(1) Operation code designations r and p form the binary representation of the registers and ports involved.(2) The dot under the appropriate flag bit indicates that its contents is subject to change by the instruction it appears in.

No operation performed.

Miscellaneous

<sup>(3)</sup> References to the address and data are specified in bytes 2 and/or 1 of the instruction.

<sup>(4)</sup> Numerical subscripts appearing in the operation column reference the specific bits affected.

### Instruction Set (cont)

### **Symbol Definitions**

| Symbol         | Description                       |

|----------------|-----------------------------------|

| A              | Accumulator                       |

| AC             | Auxiliary carry flag              |

| addr           | Program memory address (12 bits)  |

| B <sub>b</sub> | Bit designator (b = 0-7)          |

| BS             | Bank switch                       |

| BUS            | Bus port                          |

| С              | Carry flag                        |

| CLK            | Clock signal                      |

| CNT            | Event counter                     |

| D              | Nibble designator (4 bits)        |

| data           | Number of expression (8 bits)     |

| DBF            | Memory bank flip-flop             |

| F0, F1         | Flags 0, 1                        |

| ı              | Interrupt                         |

| Р              | In-page operation designator      |

| IBF            | Input buffer full flag            |

| Рр             | Port designator (p = 1, 2 or 4-7) |

| PSW            | Program status word               |

| Symbol | Description                                                                    |

|--------|--------------------------------------------------------------------------------|

| Rr     | Register designator (r = 0, 1 or 0-7)                                          |

| SP     | Stack pointer                                                                  |

| T      | Timer                                                                          |

| TF     | Timer flag                                                                     |

| T0, T1 | Testable inputs 0, 1                                                           |

| Х      | External RAM                                                                   |

| #      | Prefix for immediate data                                                      |

| @      | Prefix for indirect address                                                    |

| \$     | Current value of program counter                                               |

| (x)    | Contents of external RAM location                                              |

| ((x))  | Contents of memory location addressed by the contents of external RAM location |

| +      | Replaced by                                                                    |

| OBF    | Output buffer full flag                                                        |

| DBB    | Data bus buffer                                                                |

| AND    | Logical product (logical AND)                                                  |

| OR     | Logical sum (logical OR)                                                       |

| XOR    | Exclusive-OR                                                                   |