SYSTEMS TRAINING PART II

### FLUKE

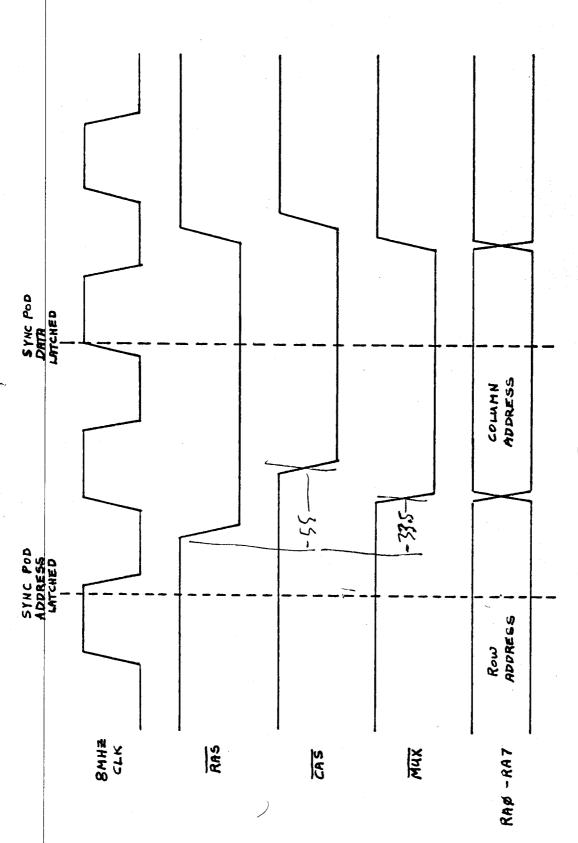

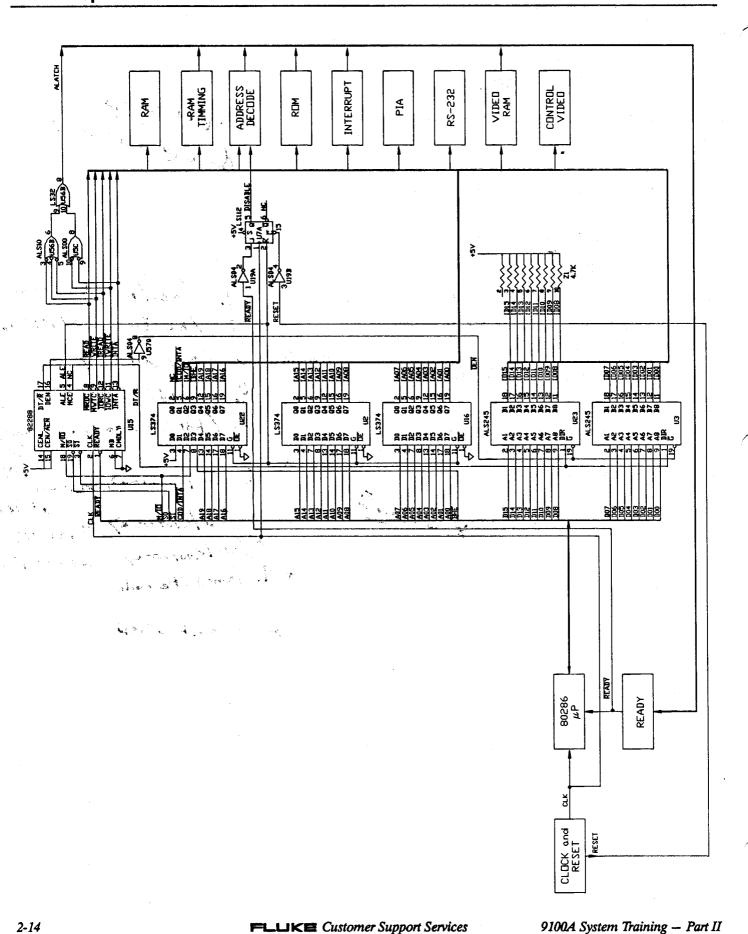

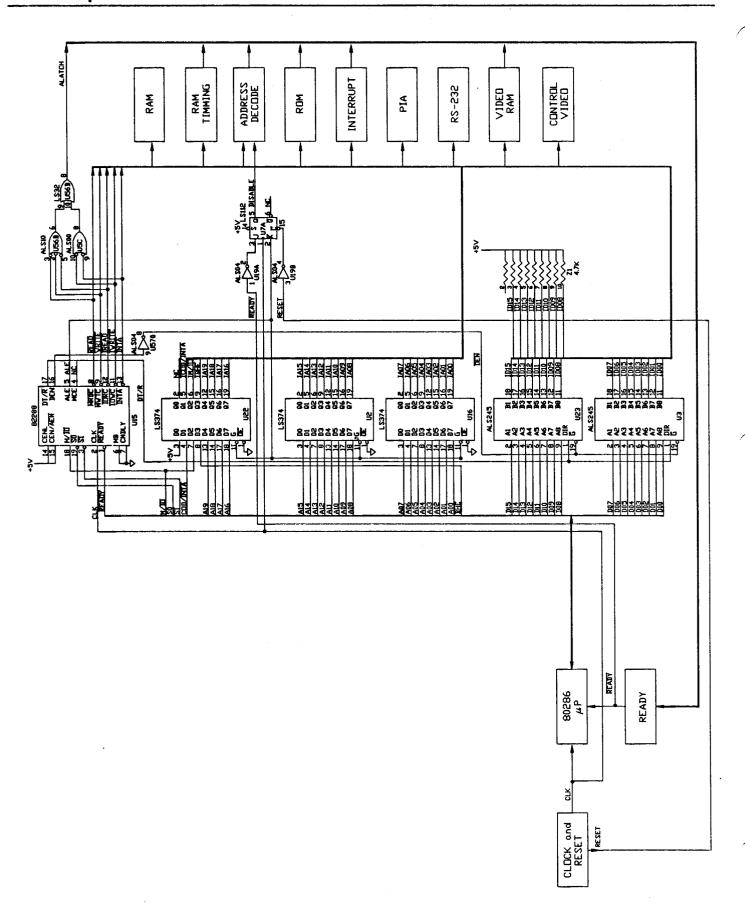

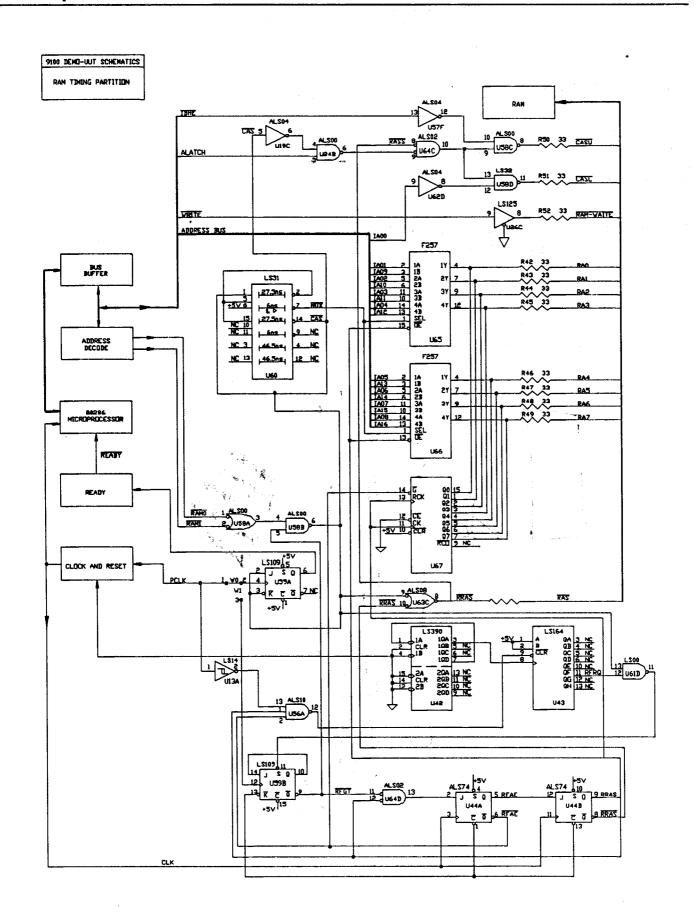

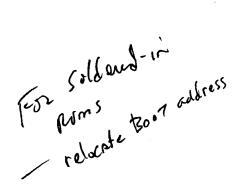

DYNAMIC RAM ADDRESS TIMING

# 9100A FUNCTIONAL TEST AND STIMULUS FLOW FOR MDE

NO.

L0046A

TITLE

#### 9100A Series Digital Testers A0266C 9132A Memory Interface Pod A0321A Microprocessor Pod Adapters A0355B Vector Output I/O Module A0357A 9100A Synchronizing I/O Module and A0367A Probe with "Int" Mode 9132A-68030 Processor Support Pkg. A0372A 9132A-64180 Processor Support Pkg. A0373A 9132A-68020 Processor Support Pkg. A0374A 9132A-80386 Processor Support Pkg. A0379A 9132A-80386SX Processor Support Pkg. A0380A 9132A-68000 Processor Support Pkg. A0384A 9132A-80486 Processor Support Pkg. A0385A 9132A-7810 Processor Support Pkg. A0386A 9132A-80286 Processor Support Pkg. A0387A 9100A-030 9010 to 9100A Programming A0392A Translator IEEE 488/Plus Option 9105A-015/ A0393B 9100A-015 UGK 9132A-68HC11 Processor Support Pkg. A0406A Using Multiple I/O Modules For Driving L0045A

Patterns and Gathering Signatures

GFI Database

Putting a Software Switch Into Your

| 第一個 | 100mm | 100m

#### APPLICATION NOTES

| TITLE                                                                                                | NO.    |

|------------------------------------------------------------------------------------------------------|--------|

| Determining the Suitability of Digital<br>Designs For Testing With The 9132A<br>Memory Interface Pod | B0186A |

| 9100A Testing of a CGA Card With The Vector I/O Module                                               | B0192A |

| Developing Test Vectors For a Video<br>Controller Chip                                               | B0200A |

| Testing DMA Circuitry on the IBMPC-AT                                                                | A0350A |

| Adding IEEE-488 Instruments to The 9100A Digital Test System                                         | A0349A |

| 9100A Production Testing                                                                             | L0030A |

#### **Creating a UFI Database**

UFI is designed so that an experienced technician can use the 9100A's GFI pin testing capability and decide from the results were to test next. The UFI operator may use a combination of functional tests, keypad commands, and UFI to troubleshoot a UUT. You already have a number of functional tests designed for the Trainer UUT and you are now familiar with testing from the operators keypad. In this section, you will learn all the steps involved in building a UFI database.

To illustrate the steps required in creating a UFI database, we are going to use the Trainer UUT and together perform all the steps to develop UFI for the data bus out from the microprocessor.

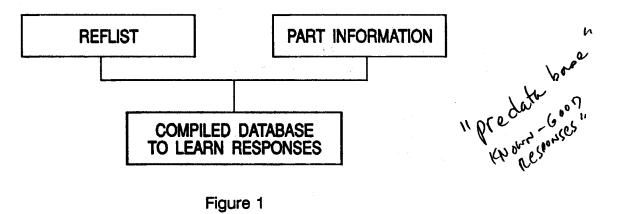

Figure 2-1 shows the structure of the UFI database used to learn responses. It contains the following types of information:

- Part Descriptions

- Reference Designator List (REFLIST)

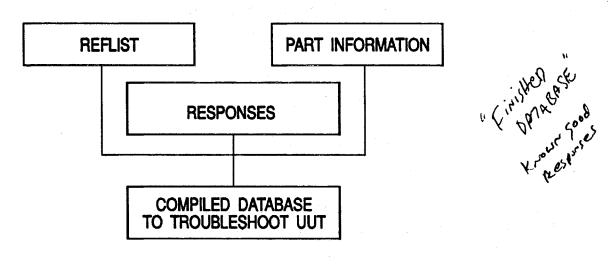

Figure 2-2 shows the structure of the UFI database used for troubleshooting. It contains the following types of information:

- Part Descriptions

- Reference Designator List (REFLIST)

- Stimulus Program Responses

Per list 1400

ex. 02-7410

ex. 02-7410

ex. 02-7410

Per list measurement

- Neso cists measuremen

#### Creating a UFI Database

- 1. Enter Part Descriptions

- 2. Enter Reference Designator List

- 3. Compile to Learn Responses

- 4. Develop Stimulus Routine

- 5. Write Stimulus Program

- 6. Learn Stimulus Responses

- 7. Compile to Troubleshoot UUT

8. Perform a Summary

9. Test — test bad

graphical representations

of datebase

(romostry rom)

6

2608

Go Here

Oursnows

Oursnows

Technical Questions

A STATE OF A STATE OF

S. Frank

# 9100 SERIES • SOLUTIONS

9100A SYSTEMS TRAINING - PART II

# FLUKE

©1990, John Fluke Mfg. Co., Inc. All Rights Reserved Litho in U.S.A.

John Fluke Mfg. Co., Inc.

625 . . . . . . .

The same

Customer Support Services P.O. Box 9090 MS 239D Everett, Washington 98206 (206) 347 6100 or (800) 44-FLUKE Ext 73

Rev. October 31, 1990

# **Table of Contents**

#### Section 1

#### 9100A Part I Review

#### Section 2

#### **UFI: Microprocessor Emulation**

| Executing a Functional Test 2-3           |

|-------------------------------------------|

| Troubleshooting From a Functional Test2-5 |

| Creating a UFI Database                   |

| Learn Responses                           |

| Step 1: Part Descriptions 2-10            |

| Step 2: Reference Designator File 2-11    |

| Step 3: Compile to Learn Responses 2-13   |

| Step 4: Develop the Stimulus Routine 2-15 |

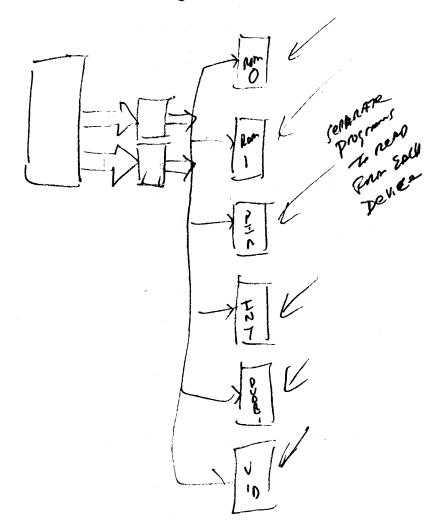

| Step 5: Stimulus Programs 2-17            |

| Step 6: Stimulus Response Files 2-21      |

| Step 7: Compile To Troubleshoot 2-37      |

| Step 8: Summary File 2-37                 |

| Step 9: Testing 2-38                      |

| Lab Exercise                              |

| Address Bus                               |

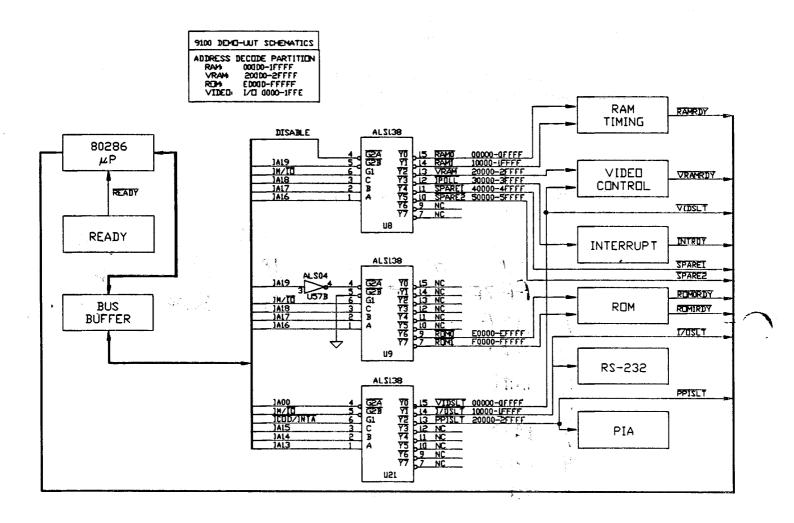

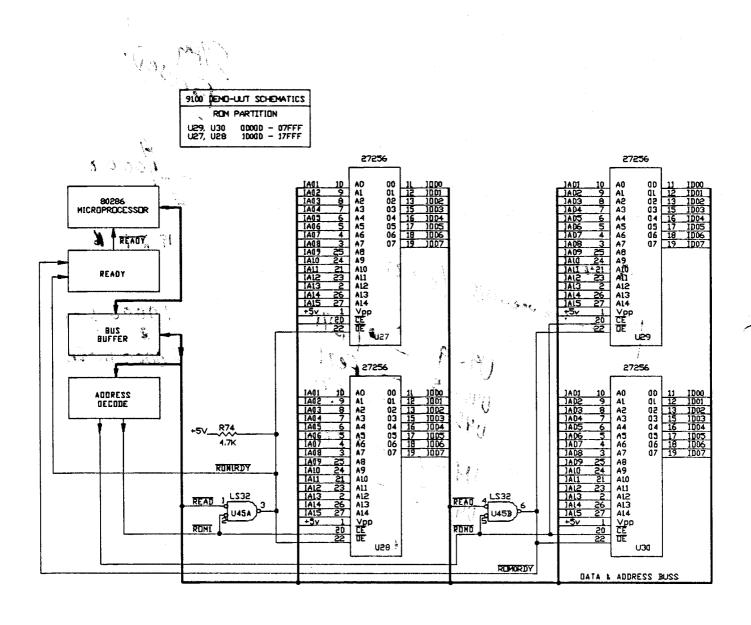

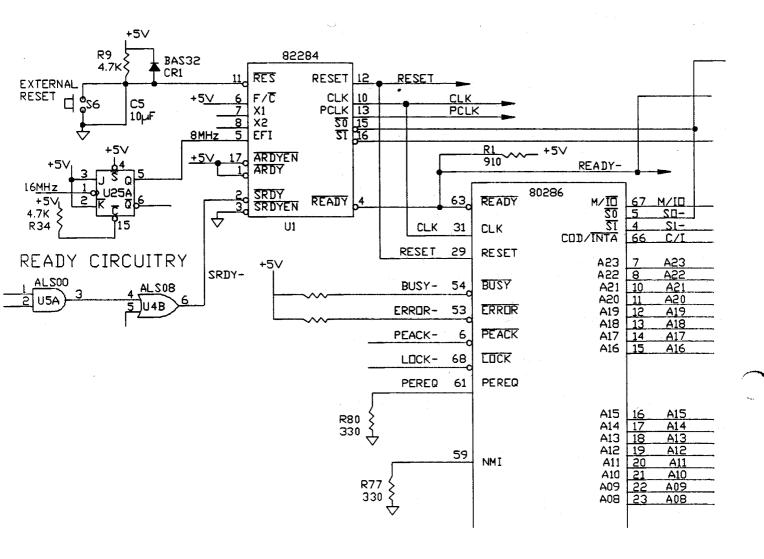

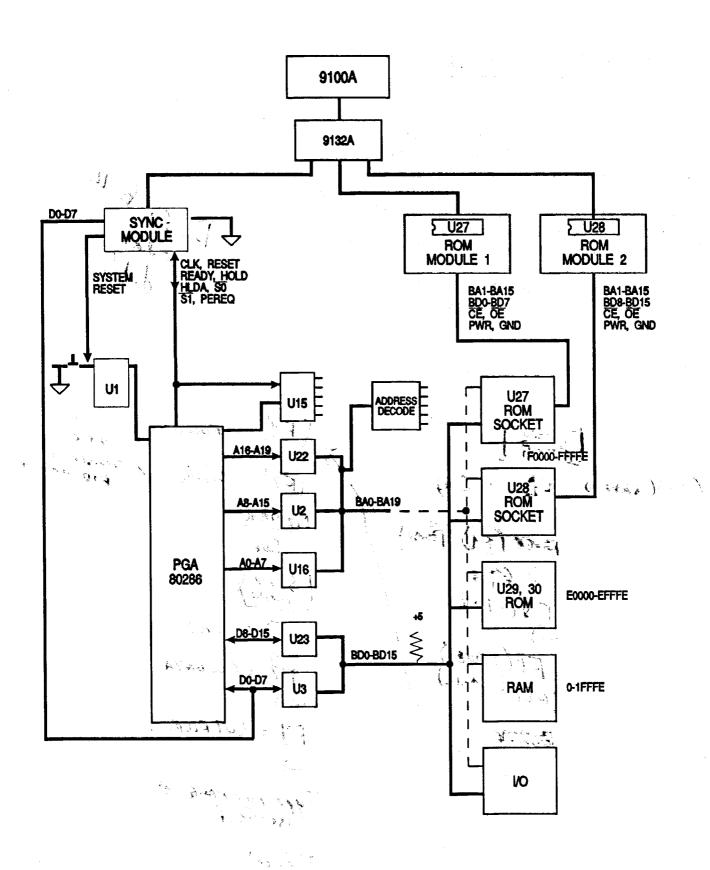

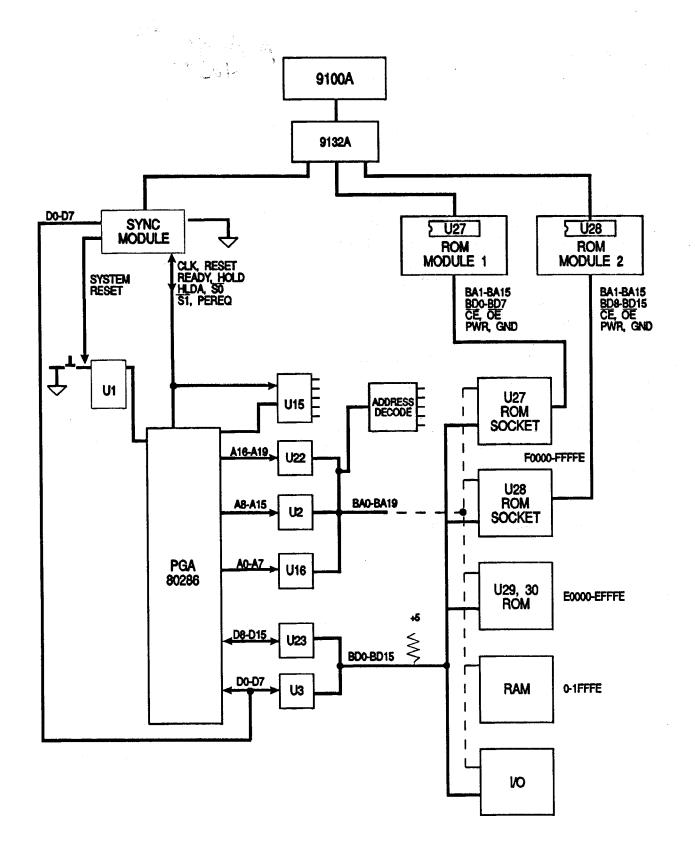

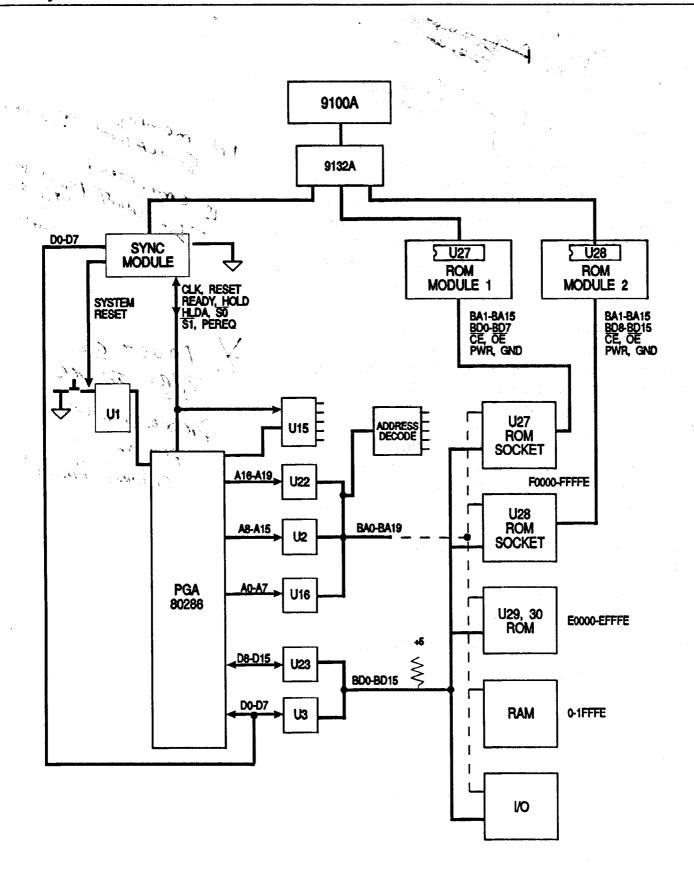

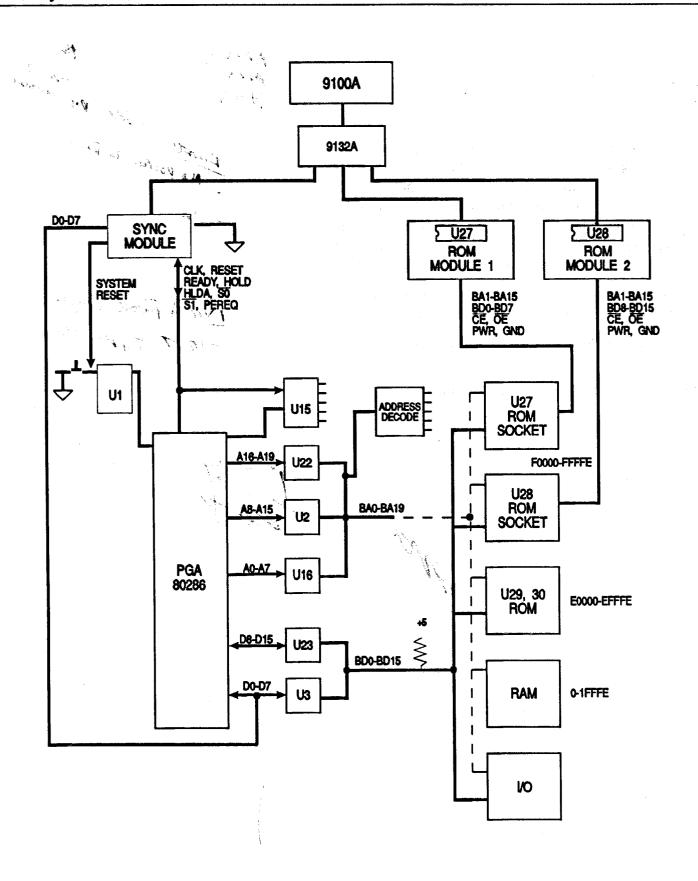

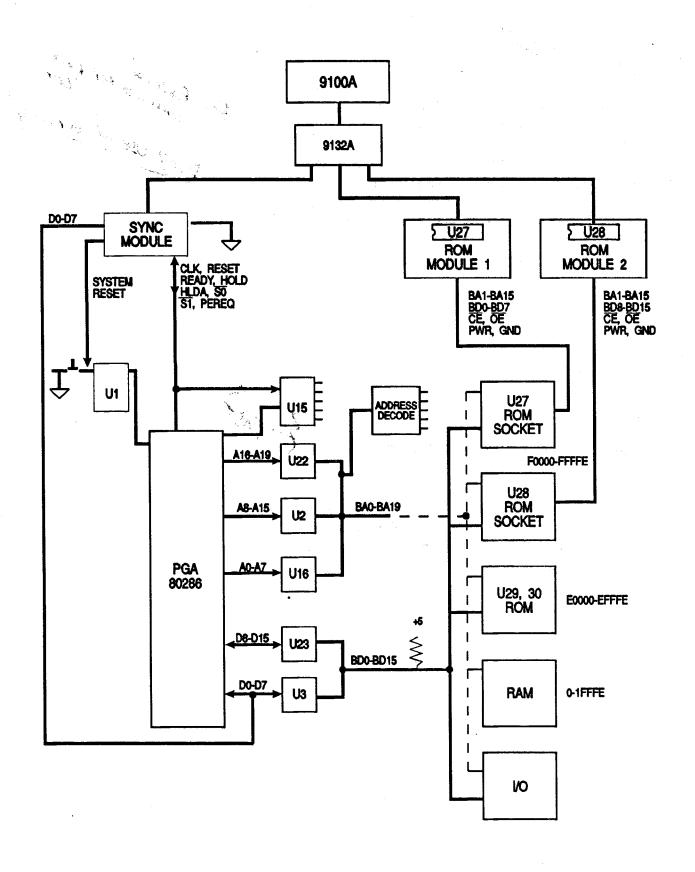

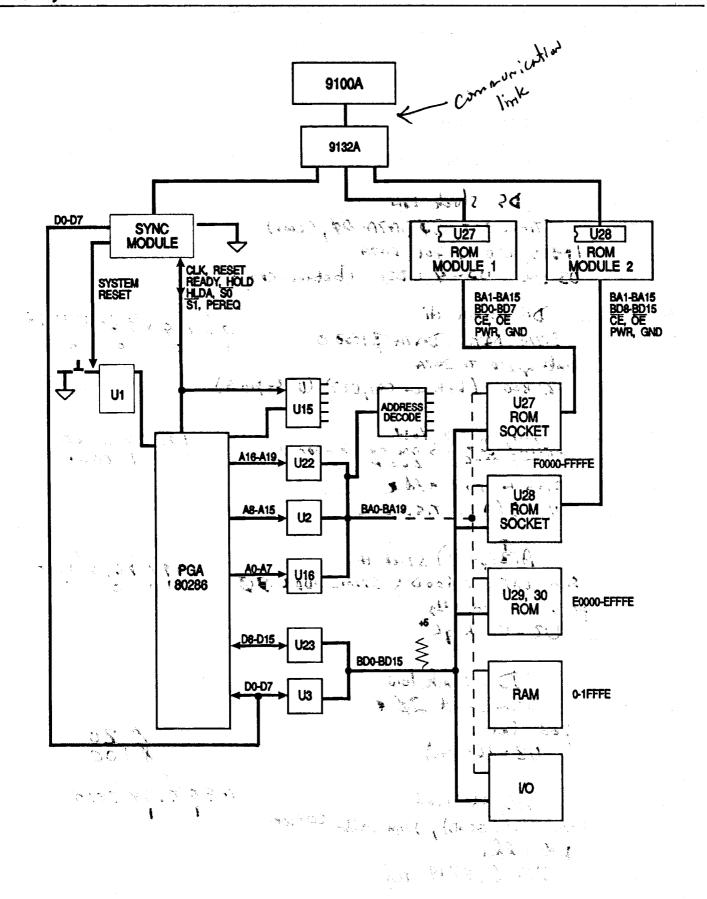

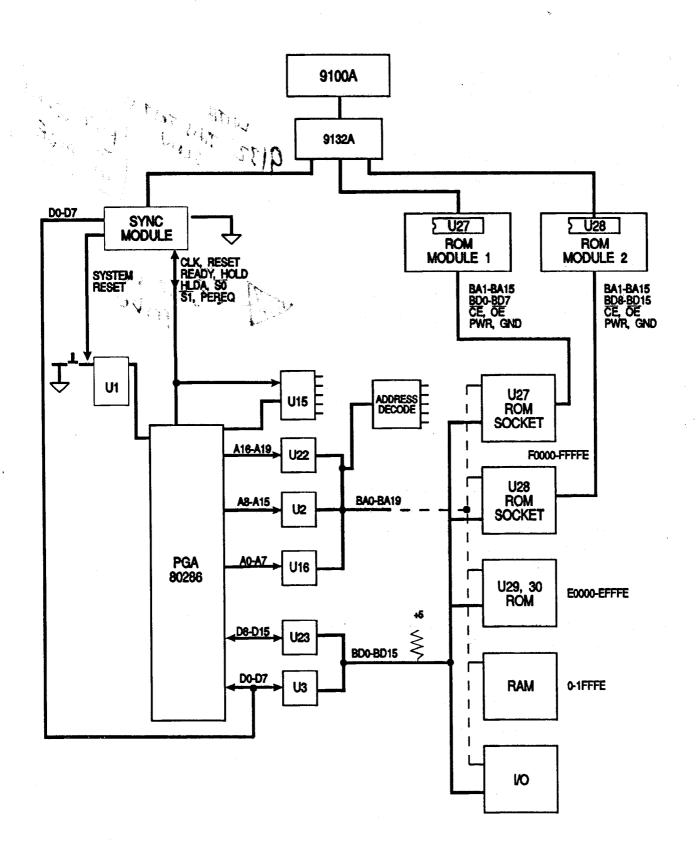

| ROM Address Decode Circuit 2-43           |

| ROM 1 Data Bus                            |

| RAM RAS Addressing 2-47                   |

| Section 3  GFI: Microprocessor Emulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                        |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |  |

| Section 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                        |  |

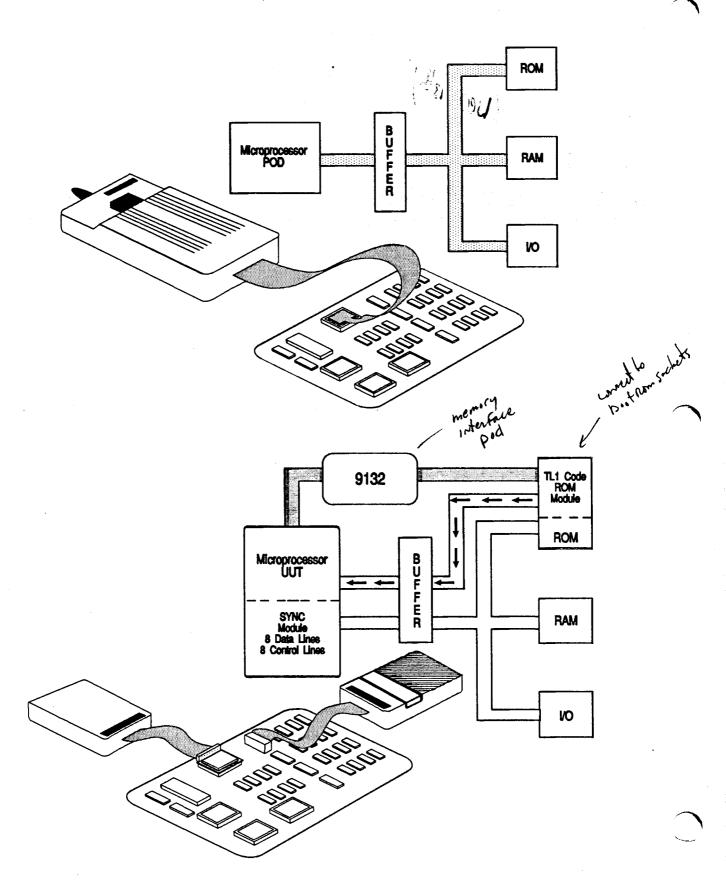

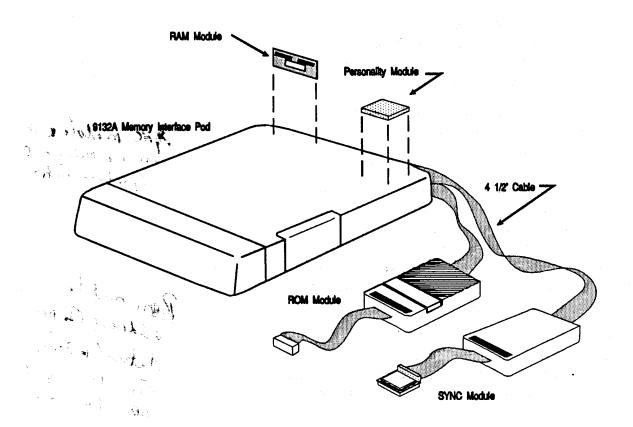

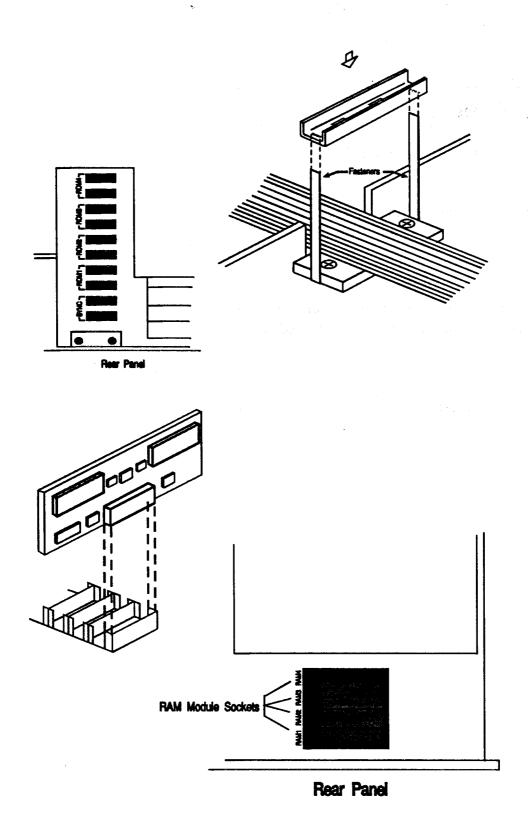

| Memory Emulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Overview                               |  |

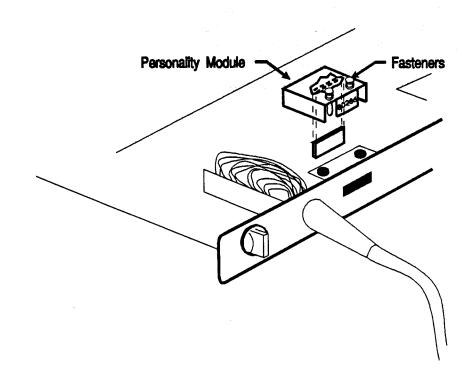

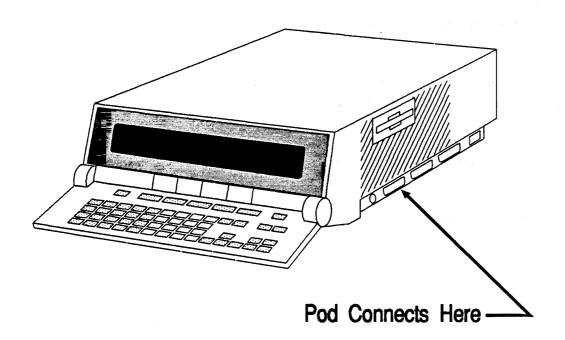

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Description of the Pod                 |  |

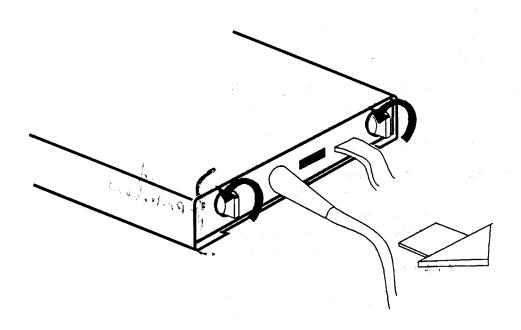

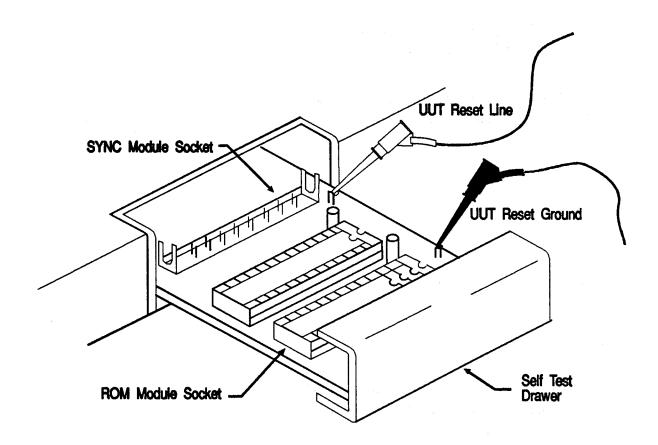

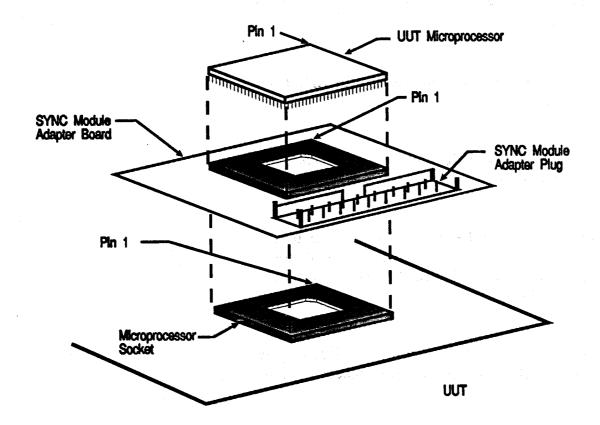

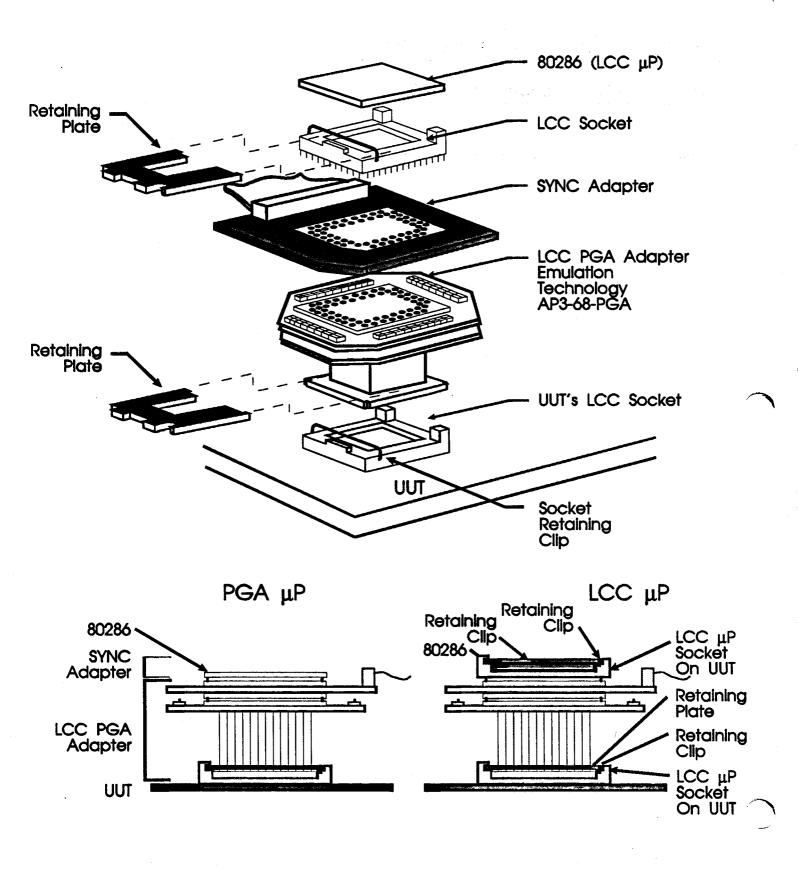

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Installation of the Pod and Modules4-9 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Master User Disk 4-15                  |  |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Pod Self Test                          |  |

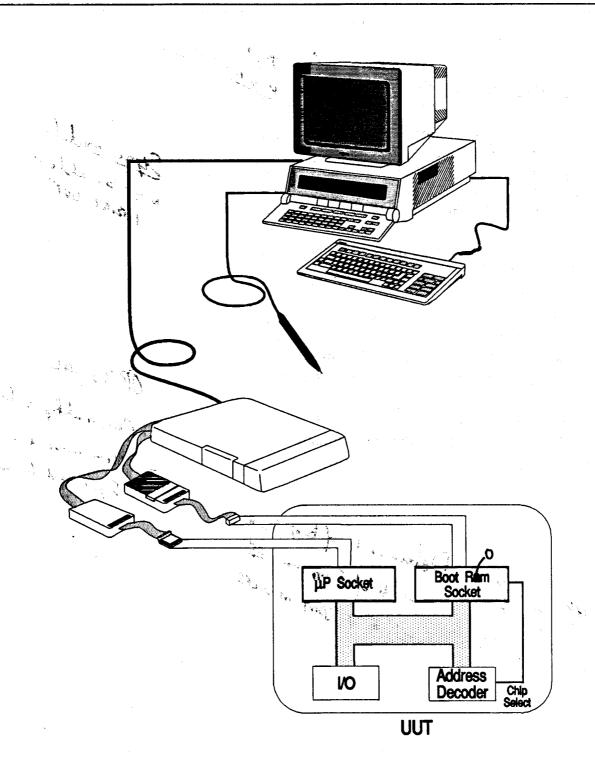

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Connecting the Pod to the UUT 4-19     |  |

| green and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Sync Module Connection to the UUT 4-19 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Reset Connection to UUT 4-29           |  |

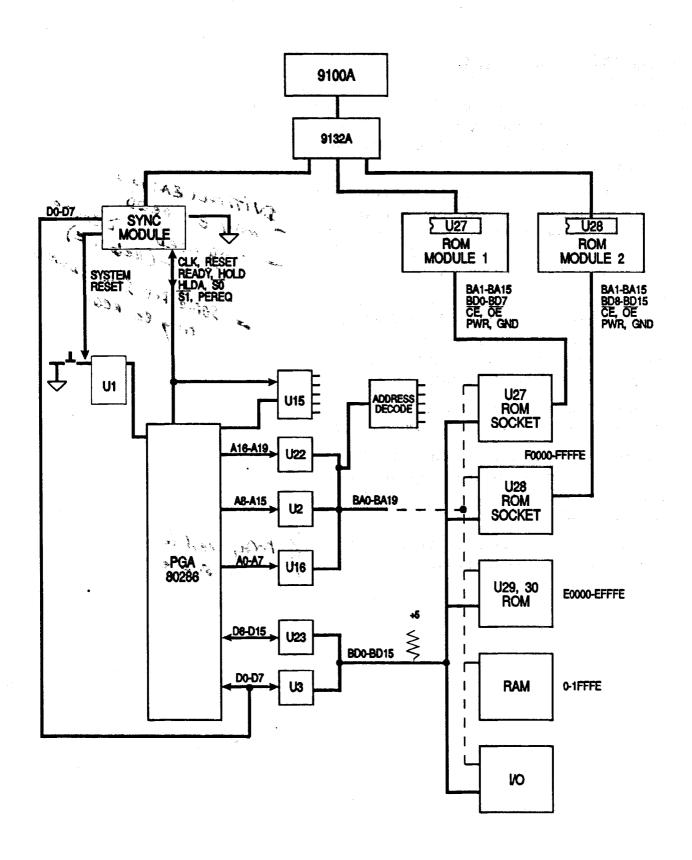

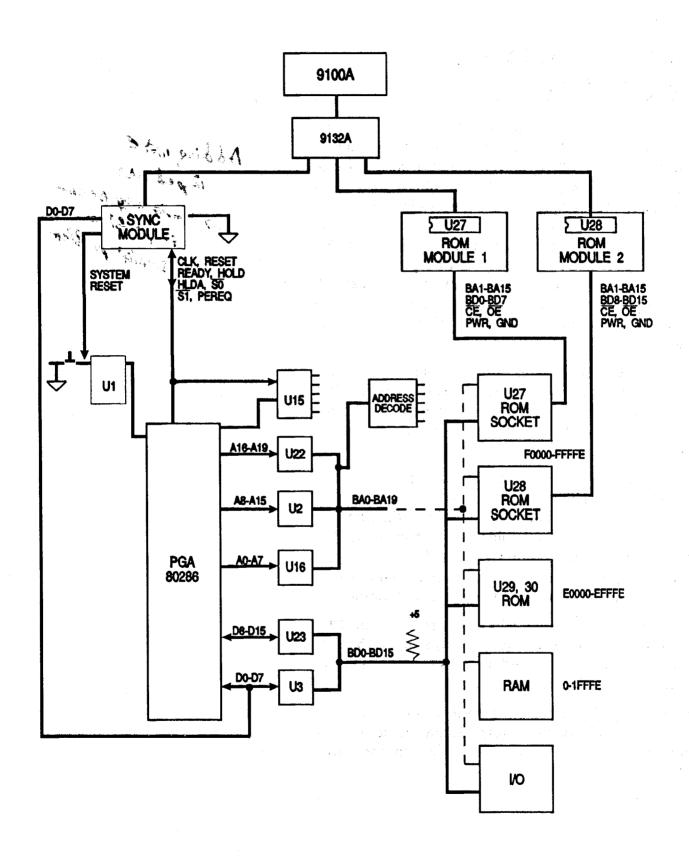

| 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ROM Module Connection to UUT 4-33      |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Pod Setup                              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SETUP Program 4-47                     |  |

| , i essenti di a, e i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Calibration of the Probe 4-49          |  |

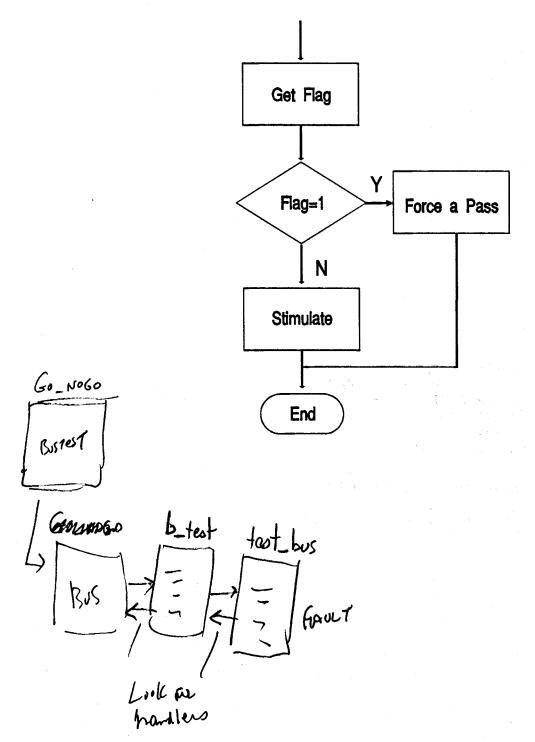

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Bus Test                               |  |

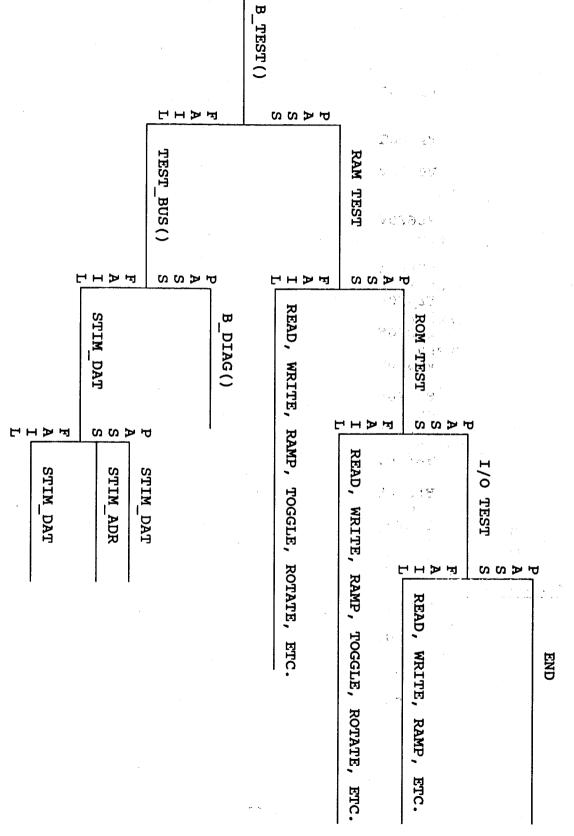

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>B_TEST</b>                          |  |

| Appropriate Control of the Control o | TEST_BUS                               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | B_DIAG 4-55                            |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Exercise 4-1                           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Fault Isolation                        |  |

| 1        | ,                                   |

|----------|-------------------------------------|

|          | STIM_ADR                            |

|          | QWK_RD 4-61                         |

| :        | QWK_WR 4-63                         |

|          | Exercise 4-2                        |

|          | Testing the UUT RAM                 |

|          | RAM Fast Test                       |

|          | HyperRAM Test                       |

|          | RAM Full Test 4-67                  |

|          | Exercise 4-3                        |

|          | Gathering Signatures 4-71           |

|          | ROM Test                            |

|          | Exercise 4-4                        |

|          | Troubleshooting Hints               |

|          | Problems Due to a Marginal UUT 4-79 |

|          | GO_NOGO Program                     |

| ction 5  |                                     |

| UFI: Mer | mory Emulation                      |

| ction 6  |                                     |

|          |                                     |

Appendix A

Section 5

Section 6

Glossary

**Using Diagnostics**

# Section 1 9100A Part I Review

Registray pod 9132 FT pod

# Section 2 UFI: Microprocessor Emulation

The exercises you perform in this section illustrate the capabilities and ease of use of the 9100A Series Digital Test Station after software development is complete. At the completion of this course, you will have performed all the necessary steps to recognize faults on the demo UUT and troubleshoot them using the Unguided Fault Isolation (UFI) and immediate mode methods.

-> TOOL TO HELP I DESTIFY I'F NOORS ARE GOOD OR BAD

#### **Executing a Functional Test**

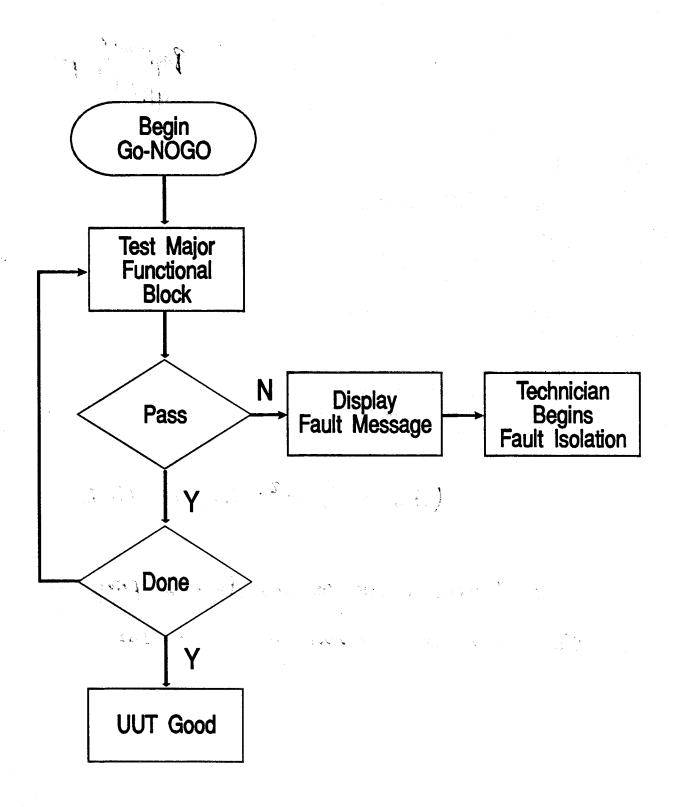

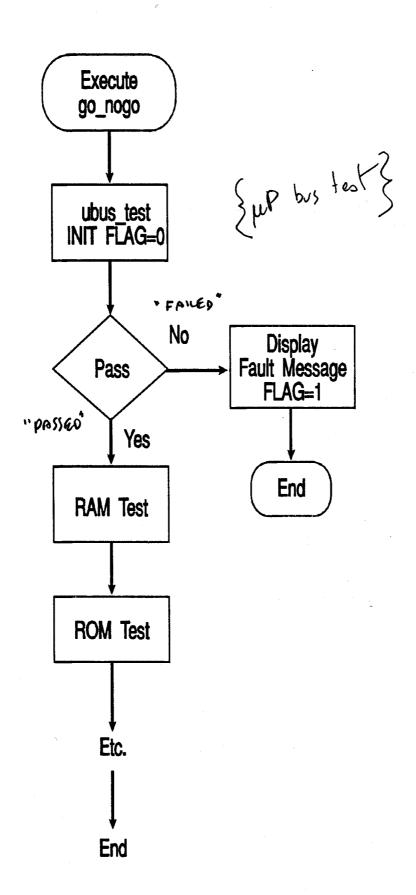

The software you are about to execute follows the flow illustrated on the previous page. The exercise performs a major functional test on the UUT. If the test passes, the UUT is either declared good, or another major functional block will be tested. If a major functional block fails, the error is displayed. This method is commonly referred to as "go-nogo" testing. The technician can then begin fault isolation.

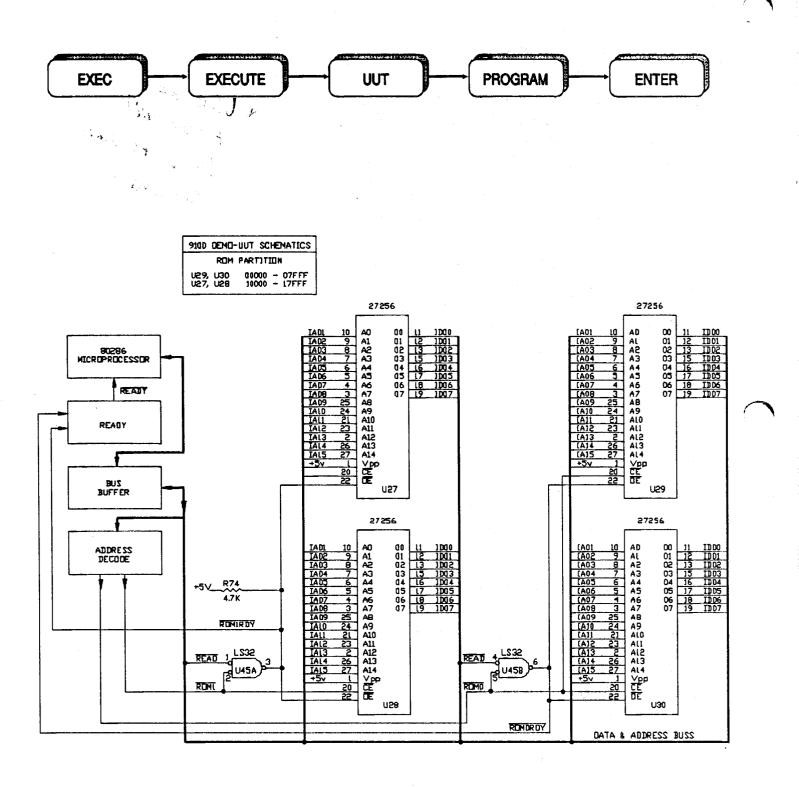

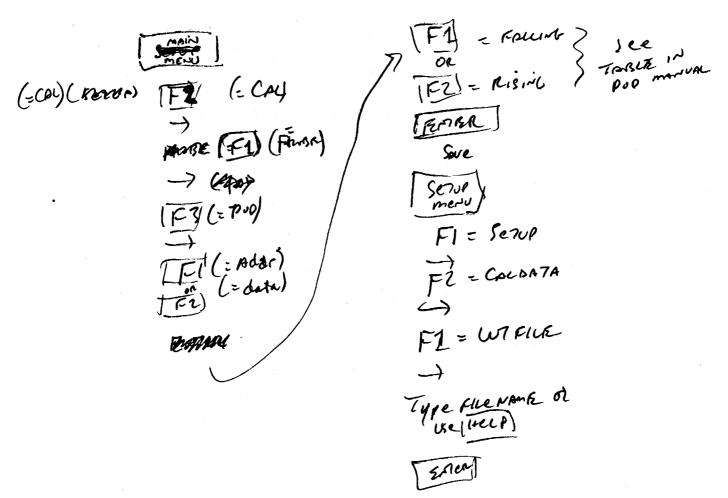

With no fault switches set on the Demo-Trainer UUT (Switch pack 1, switches 1 through 8 "on", all other switches "off"), press on the 9100A Applications keypad. The Mainframe displays the following menu:

EXEC UUT PROGRAM

Select the UUT name "CD" using HELP

Select the PROGRAM name "GO\_NOGO" using FEP.

The following should now be displayed on the Mainframe:

EXEC UUT CD PROGRAM GO\_NOGO

Begin the program execution by pressing on the 9100A Applications keypad.

During execution of the program, a go-nogo test will be run on the ROM circuit. U27, U28, U29, and U30 are functionally tested. Since no errors are reported, the ROM circuit is declared "good" by simply ceasing execution (No News is Good News!).

\* USE OF will probe technician leep (acused

# Troubleshooting From a Functional Test

To illustrate what happens when a fault is encountered, set fault switch SW1-2 to it's fault position (switch off) then execute the program as shown in the previous exercise.

Now during program execution, a fault is detected while testing the U27 functional block. The following error message will appear on the Mainframe display:

Testing from F0000 to FFFFE all ROM data bits stuck high

To continue the test, press on the 9100A Applications keypad.

Notice the program resumes the go-nogo test until complete.

From the error message we see that since all data lines are stuck, U27 most likely has a control line problem. This could be caused by several things but lets start at the source of the problem by performing a test of the ROM device itself.

Since all of the UFI programs and responses have been done for us, we'll begin by performing a UFI test of control lines at U27.

Press the GFI key on the Applications keypad. The following should be displayed:

RUN GFI UUT CD REF PIN Select REF "U27" and PIN "22" (Pin 22 is one of the control lines at U27). The display should look like this:

RUN GFI UUT CD REF U27 PIN 22

Press FIFE.

What were the results? By analyzing the result, what would be the next logical step?

Find the fault by backtracing.

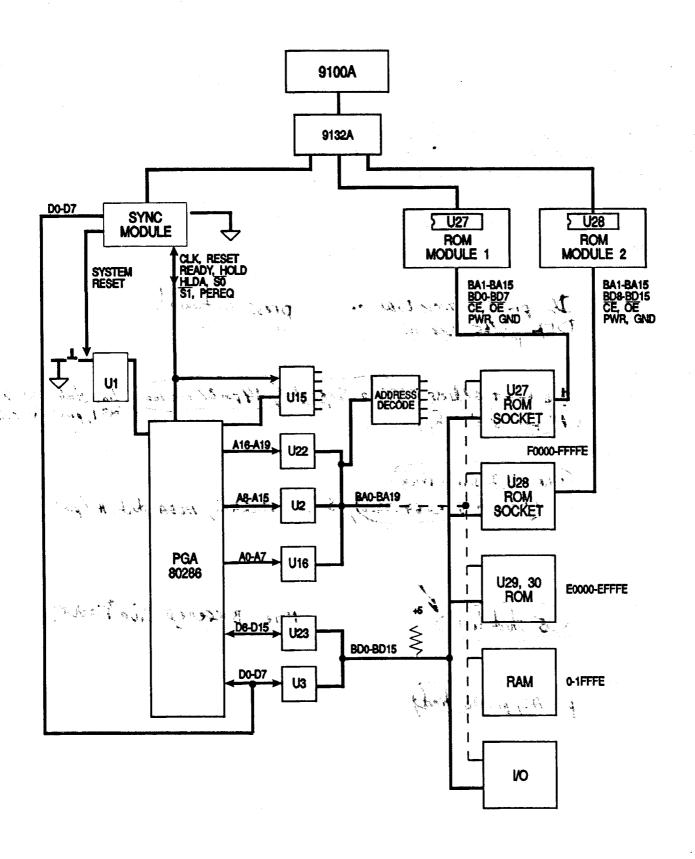

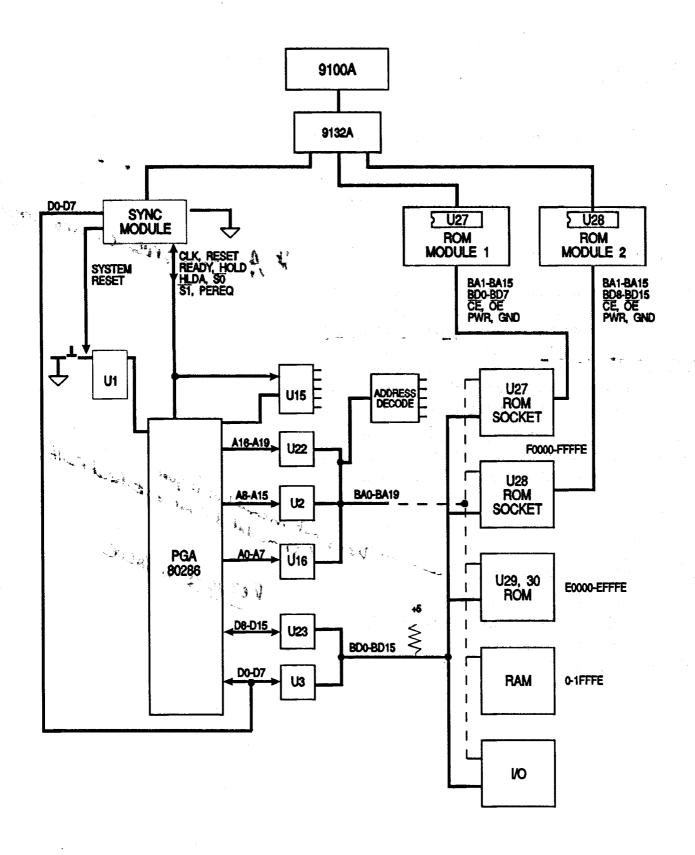

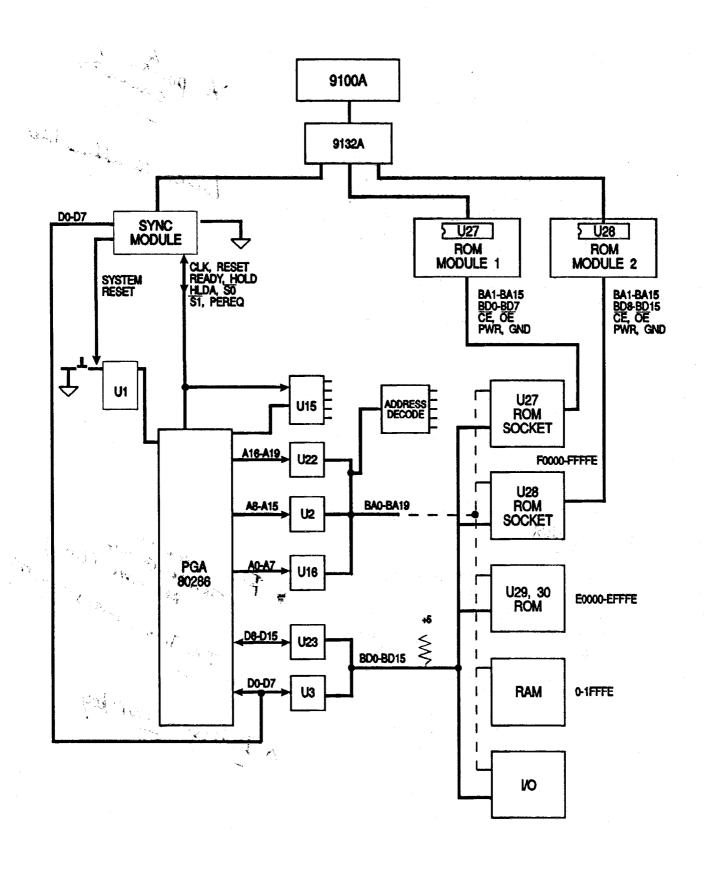

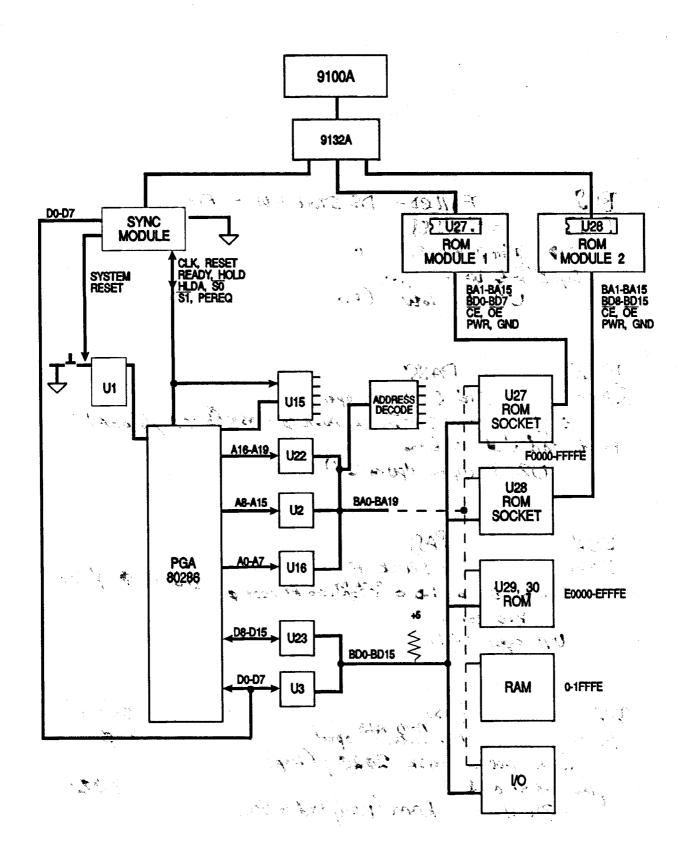

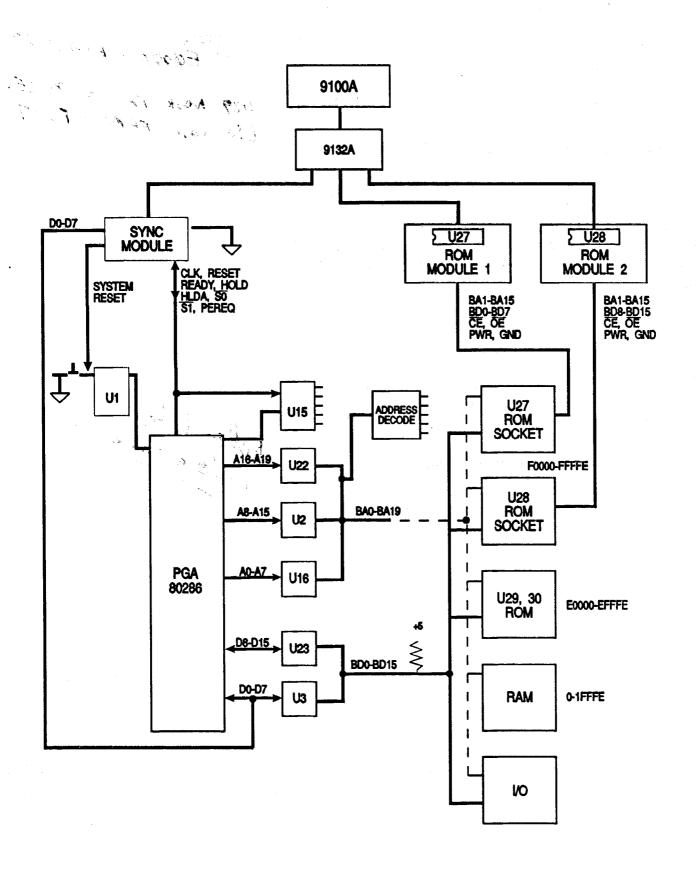

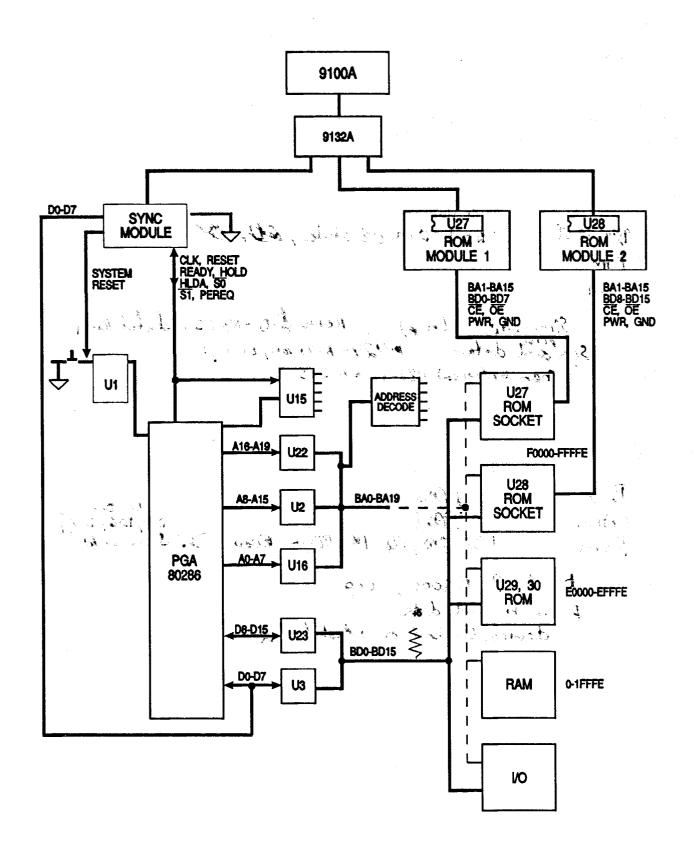

Figure 1

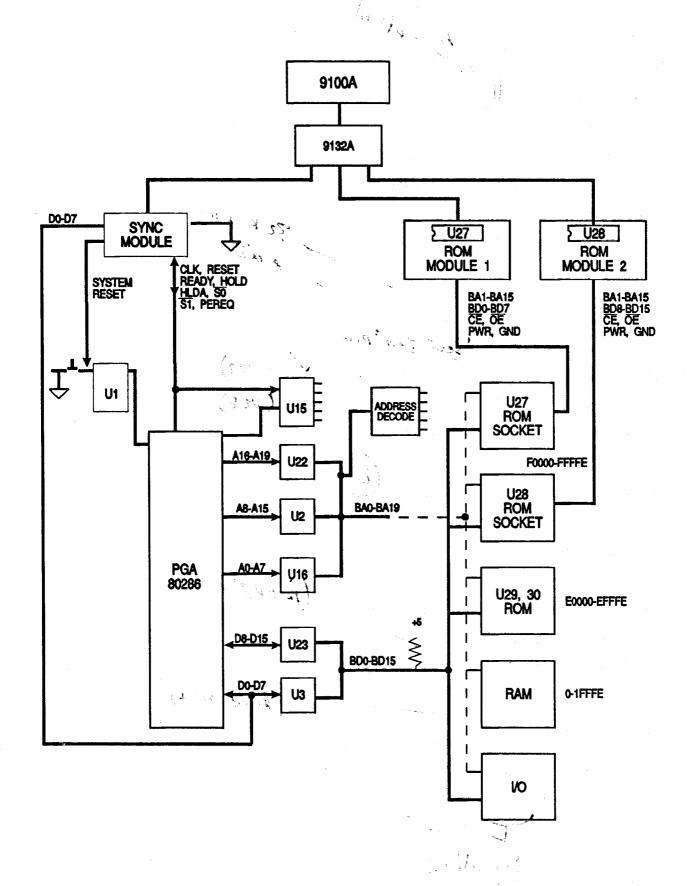

Figure 2

#### **Part Description**

The part description identifies the package type, number of pins, and the function of each pin (such as input or output). The related input pins can be designated for each output.

# (IN PART LIBRARY)

#### Reference List

The Reference Designator List (REFLIST) identifies the part reference (U3), the type of part (74245) and the measurement device (I/O MODULE) used to test that reference.

#### Compile to Learn Responses

Once the part descriptions and reference designator list are completed, you must perform a compile to learn responses operation to initialize the database.

#### Response File

The Stimulus Program Response file contains the known good responses of nodes which the corresponding stimulus program stimulates.

#### Stimulus Programs

In addition to the items in the database, UFI requires a set of TL/1 stimulus programs. The programs are used to generate the responses stored in the database. Each stimulus program will have a corresponding stimulus response file.

#### **Compile to Troubleshoot**

Stimulus programs, stimulus responses and reference designators and the UFI database are all stored in the UUT directory. The part descriptions are stored in a part library (PARTLIB) at Userdisk level for use by all UUTs.

On the facing page is a list of steps that must be done to create a UFI database for troubleshooting. The only item that is optional is the Summary. All other items must be performed in the order presented.

#### Learn Responses

Before you can learn responses for UFI or GFI you must first set up the database with some initial information. In the following exercise, Steps 1, 2, and 3 are necessary to create a database usable by the Learn Responses Utility.

#### **Step 1: Part Descriptions**

List the part types and references involved when the microprocessor is putting data out to the bus.

EDIT: /hdr/partlib

TYPE: LIBRARY

A directory of part descriptions already in the parts library (PARTLIB) are shown. The types are generic in that a 74245 is used for 74LS245, 74ALS245, 74HCT245, etc. because the pin configuration is the same.

Check the directory for all parts that you have listed.

Are the parts in the library?

To illustrate how to create a part description, let's edit a part called "dummy".

EDIT: dummy

TYPE: PART

How is the pin configuration selected?

How is the function of each pin selected?

QUIT editing the part "dummy" and when asked if you wish to save your changes, select NO.

Where did you return to?

#### Step 2: Reference Designator File

The Reference Designator (REFLIST) file is used by GFI/UFI to cross reference the part to the reference designator. It also indicates which measurement device to use for GFI/UFI.

Edit the Reference Designator List:

EDIT: /hdr/trainer/reflist TYPE: REF

Are all of the required references listed and are the correct testing devices selected?

QUIT editing the REFLIST. Where did you return to?

PUT POLS/GALS LIBRARY

(UI, UZ....)

(UU7 dependent)

¥. }

Qt Wi

100

#### /HDR/TRAINER/MICRO\_DATA

# UUT COMPILER (UFI)

Processing UUT reflist and parts...

0 errors

Writing string table...

Writing part table...

Writing ref table...

Writing node table...

Press Msgs key to continue

#### Screen 1

#### **Compile to Learn Responses** Step 3:

At UUT directory level F3 is used to perform a compile.

Press [F3]. The following prompt will appear: COMPILE database to TROUBLESHOOT UUT

Field Select LEARN RESPONSES. Press RETURN.

You are now prompted to Field Select UFI or GFI.

Select UFI. Press RETURN to compile the database.

If the compile is successful, the screen 1 will be displayed on the programmers display.

Press Msgs on the programmers keyboard.

IMPORTANT: The Step 3 sequence must be performed any time there is a change to the parts library or the reference designator file.

Compiles always done @ UUT level

1. har/partlib Eje: Lisany 2. / hdr/fwu Nomes/reflist Type REF

(Compile) 3. / hdr/KWTNOME>

\* 4. immediate made

5. / hdr/but mme>/sprog wave) 6. /hdr/(wor name)/(prog. name)

Type: RESPONSE

7. /hdr/Kuurnone> Tyee: WT 8. /har/ (ungraphe) Tupe: UUT

\* - mich often

\* CXACT SAME HAVE

#### Step 4: Develop the Stimulus Routine

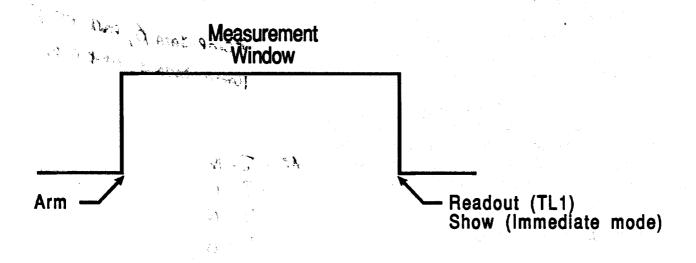

A Stimulus routine controls the beginning and end of a measurement period and the activity on the node that causes a predictable and repeatable response. The stimulus routine also determines the direction of data flow. The stimulus routine NEVER evaluates the results of the measurement if it's used for UFI or GFI.

Stimulus routines are most often developed in the immediate mode.

#### **Data Stimulus Commands**

- rampdata

- toggledata

- rotate

#### **Address Stimulus Commands**

- rampaddr

- **■** toggleaddr

The next step in our UFI process is to develop our stimulus routine for the data bus out. This step can be done at any time.

Write down the steps developed in immediate mode to stimulate the data bus from the microprocessor.

**ARM**

**SHOW**

DATA BUS EXAMPLE

ormans 16 x 3 = 48 responses

\* Important to Liver signal direction Ca basketrace

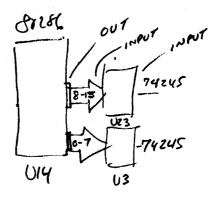

U14 - 80286 U23 - 74 ALSZUS PARTLIB U3 - 74 ALSZUS

INFO Key Cocard Mind related pind related pind related pind roughly order must not be persent to the property of the persent to the persent of the persent o

Screen 2

#### Step 5: Stimulus Programs

Once the stimulus routine has been developed, you can begin writing the stimulus program.

In some instances, certain inputs are driven by more that one source. If this is the case, you need to write additional programs for each of those sources.

When writing a stimulus program used for more than one node, be sure that the measurement for each node is unique. For example, when you are testing a RAM chip, you may inadvertently place the measuring device on the wrong point. If the measurements where all the same for each RAM output, the test may still pass.

It is very important that a stimulus program not simultaneously exercise multiple sources on a net. Each source capable driving any given net must have it's own stimulus program. For stimulus programs that drive the data bus, ensure that those programs clearly separate the data direction and signal sources.

#### Stimulus Program Structure

The structure of a stimulus program is broken down into three basic parts.

- Define

- Setup

- Stimulus routine

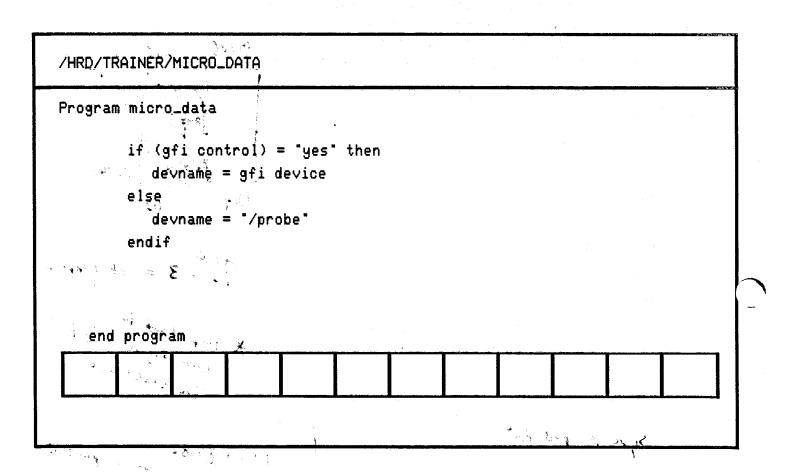

The Define portion of a stimulus program describes the measurement device to be used. Note the illustration on the facing page. If the gfi control command returns the string "yes", the measurement device will be assigned by the gfi device command. If gfi control returns a "no", the program assigns the measurement device as "/probe".

The Setup portion of a stimulus routine contains the required setups for address space, circuit initialization, pod and the measurement device setups.

The Stimulus routine contains the arm, stimulate, and readout commands. The arm command begins the measurement, the stimulus provides the activity required, and the readout command ends the measurement. Remember, The stimulus routine causes activity at a node to obtain a predictable, repeatable response.

A very important part of writing a stimulus program is naming it. Especially when they are used for UFI. Remember, the stimulus routine determines the direction of data flow. When a node fails under UFI, the name of the program that stimulated the failing node is given. The technician can use this information to aid in determinating where to test next. The following stimulus program is named "micro\_data". The name implies that the stimulus exercises data lines from the microprocessor.

Write the stimulus program:

EDIT: /hdr/trainer/stim\_0 PRORAM

TYPE:

Enter the routine that determines if the program has been called by GFI/UFI. If so, then let the database determine the measurement device. If not, assign the measurement device as "/probe".

Enter the TL/1 commands required to setup the address space, circuit, pod, and measurement device.

Enter the data bus stimulus routine that was developed in Step 4.

Debug the program.

Pryram micro-data

of (gricontrol="yes" then

devrance = gri device

devrance = "/moll"

devrance = "/moll"

Tradock permit off Court sociation

Deterie Setul Simornis

Screen 3

#### Step 6: Stimulus Response Files

The purpose of the stimulus response file is two-fold. First, the response file will contain responses obtained from a known-good UUT. Second, because the response file has the same name as the stimulus program, it provides the link between the stimulated nodes and the program that stimulates them.

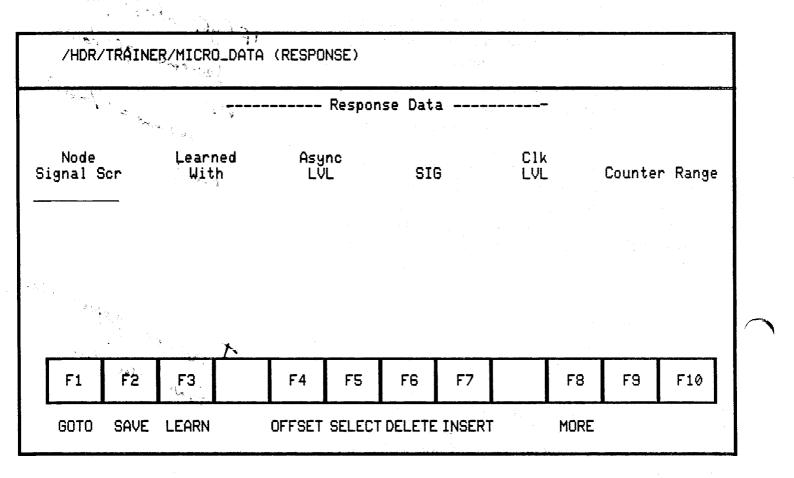

Edit the stimulus response file:

EDIT: /hdr/trainer/micro\_data TYPE: RESPONSE

The display should resemble Screen 2.

Press the info key on the programmers keyboard.

The information window is now displayed. The fields that can be modified are as follows:

#### DESCRIPTION

An optional one line description.

#### **LEARN**

Indicates if the next LEARN is for UFI or GFI. A UFI LEARN gathers responses using only the measurement device specified by the signal source pin. A GFI LEARN examines all other pins on the node and gathers responses using both measurement devices if required. Use the Field Select key to select the level desired.

#### **FOR**

Indicates the number of pins covered by LEARN. The following three options may be selected using the Field Select key:

ONE NODE The line of the edit window where cursor is located is examined. The node entered as the signal source pin is learned.

ONE REF The line of the edit window where cursor is located is examined. The signal source pin for every line that has the same reference designator is learned.

ALL REFS Every signal source in the response file is learned.

#### REPEAT

The LEARN operation is performed three times to insure that marginal timing situations are detected. This entry controls how many times the LEARN operation is repeated. A number between 1 and 99 may be entered.

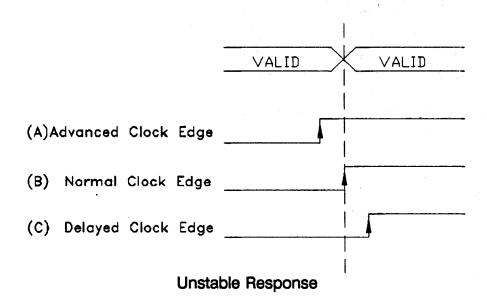

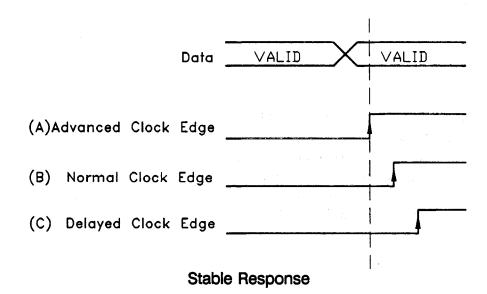

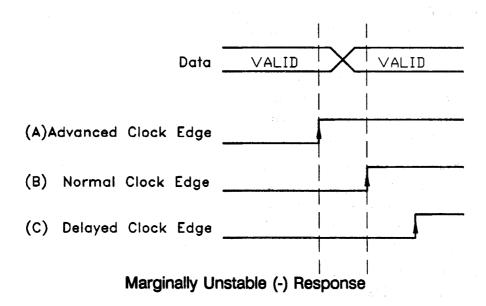

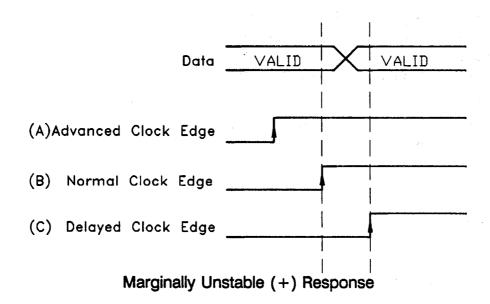

The multiple executions of the LEARN utility is used to tell if the response is:

- Stable

- Unstable

- Marginally stable

#### WRITE PROTECT

Sets/clears the write protect status of the file.

#### **SAVE**

Used to save any changes made to the Information Window.

#### Merging Responses

LEARN merges all three responses and if the same response is measured each time, the response is recorded. Signatures will be shown intensified.

- A signature recorded with a "-" indicates the advanced clock signature was different.

- A signature recorded with a "+" indicates the delayed clock signature was different.

- A "\*" indicates all three responses were different.

Screen 4

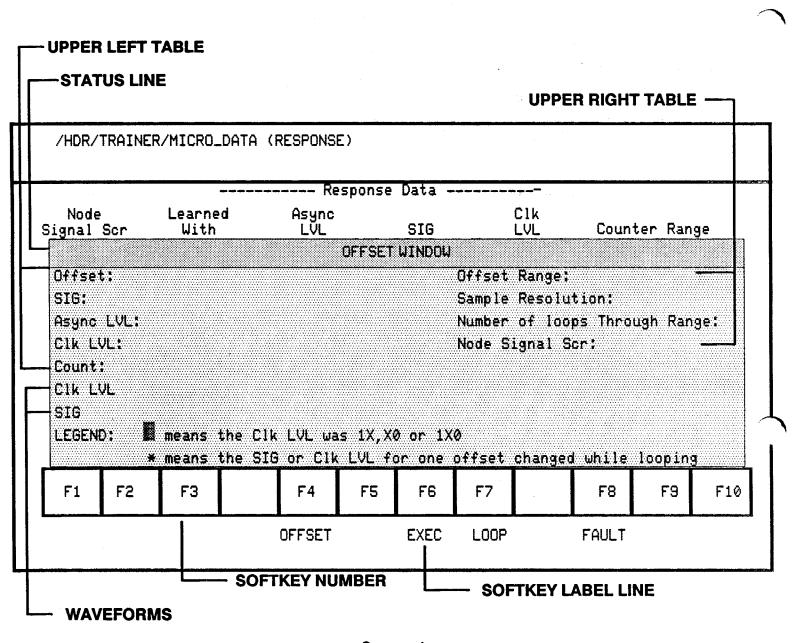

#### Response File "OFFSET" Window

Press the OFFSET softkey [54] to enable the Offset feature.

Notice that the Offset Window (Screen 4) overlays the response file editor screen.

**Upper Left Table:**

Offset: The offset for the current sample

SIG: The CRC signature for the current

sample.

Async LVL: The asynchronous level for the cur-

rent sample.

The Clocked level for the current CLK LVL:

sample.

Count: The count range for the current sample.

Upper Right Table:

Offset Range:

The range of offsets being sampled.

Sample Resolution:

The resolution between samples (1 = high resolution, 9 = low resolution).

Number of Loops Through Range:

Number of time the offset range has been swept.

Node Signal Scr:

The pin being sampled.

Re chardes:

#### Waveforms:

Clk LVL:

The clocked level waveform displays the three states: high, low, tri-state, and combinations of these states.

SIG:

The CRC signature waveform uses two symbols:

- = The parallel lines indicates that the sampled signature is the same as the previous sampled signature.

- [ The left bracket indicates the that sampled signature is different that the previous sampled signature

- ◆ The diamond shows the original offset

- † The arrow points to the current sample in the SIG waveform. It moves automatically during EXEC or LOOP. When not in EXEC or LOOP, the arrow may be moved to any sample by use of the left-arrow and right arrow keys. As the arrow is moved, the upper left table displays the response data for the pointed to sample.

#### Legend:

The Legend at the bottom of the screen shows the meaning of special symbols used in the waveforms.

The reverse video indicates the following states:

- Tri-state and high

- Tri-state and low

- Tri-state and high and low

The Upper Left Table will indicate which levels actually occured at the particular sample.

The (\*) indicates which levels actually occured at the particular sample.

| softkeys:                           |                                                                                                                           |  |  |  |  |  |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| OFFSET:                             | Toggles the offset window on and off.                                                                                     |  |  |  |  |  |

| EXEC:                               | Starts one sweep of the offset range. The TL/1 program is executed and samples taken at various offsets within the range. |  |  |  |  |  |

| _00P:                               | Causes the sweeping of the offset range to be repeated until the looping is stopped.                                      |  |  |  |  |  |

| FAULT:                              | Toggles the fault window on and off.                                                                                      |  |  |  |  |  |

| To use the Offs check for offsets   | set Window, determine which node to                                                                                       |  |  |  |  |  |

|                                     | on the appropriate line and press the softkey.                                                                            |  |  |  |  |  |

| Press the EXEC :<br>EXECUTE PR      | softkey. The following prompt appears:                                                                                    |  |  |  |  |  |

| The name of t<br>prompt line as the | he stimulus program appears on the he default.                                                                            |  |  |  |  |  |

| NOTE: The stime                     | ulus program cannot contain a setoffset                                                                                   |  |  |  |  |  |

The number entered represents nanoseconds and is biased by the value 1000000 (decimal). The default value of 999000 appears on the prompt line (1000000 - 1000) to insure the sampling begins at the lowest offset for the measurement device.

command when executing from the Offset Window.

Press RETURN. The following prompt appears:

OFFSET RANGE (ns) FROM \_\_\_\_\_\_

| /HDR/TRAINER/MICRO_DATA (RESPONSE)                                                                            |                               |                |   |              |    |     |                                   |                  |        |         |          |  |

|---------------------------------------------------------------------------------------------------------------|-------------------------------|----------------|---|--------------|----|-----|-----------------------------------|------------------|--------|---------|----------|--|

| Response Data                                                                                                 |                               |                |   |              |    |     |                                   |                  |        |         |          |  |

| Node<br>Signal So                                                                                             | r                             | Learne<br>With | d | Async<br>LVL |    | SIG |                                   | lk<br>VL         | Counte | r Range | <b>)</b> |  |

| OFFSET WINDOW                                                                                                 |                               |                |   |              |    |     |                                   |                  |        |         |          |  |

| Offset:                                                                                                       | ffset: 1000016 O              |                |   |              |    |     | Offset Range:999876 to 1000058 ns |                  |        |         |          |  |

| SIG:                                                                                                          | SIG: 00ED Sample Resolution:1 |                |   |              |    |     |                                   |                  |        |         |          |  |

| Async LVL: 1x0 Number of loops Through Range:1                                                                |                               |                |   |              |    |     |                                   | :1               |        |         |          |  |

| Clk LVL:                                                                                                      | 1                             |                |   |              |    |     | lode Sig                          | nal Scr          | :U1-1  |         |          |  |

| Count: 594 (580-628)                                                                                          |                               |                |   |              |    |     |                                   |                  |        |         |          |  |

| Clk LVL                                                                                                       |                               |                |   |              |    |     |                                   |                  |        |         |          |  |

| LEGEND: means the Clk LVL was 1X,X0 or 1X0 †  * means the SIG or Clk LVL for one offset changed while looping |                               |                |   |              |    |     |                                   |                  |        |         |          |  |

| F1                                                                                                            | F2                            | F3             |   | F4           | F5 | F6  | F7                                | . <del>-</del> . | F8     | F9      | F10      |  |

| EXECUT                                                                                                        | ING                           | <del> </del>   |   |              |    |     | A                                 | <b>.</b>         |        |         |          |  |

Screen 5

| Press RETURN. | The | following | prompt | line | appears |

|---------------|-----|-----------|--------|------|---------|

| TO            |     |           |        |      |         |

Again the number entered represents nanoseconds and is biased by the value 1000000 (decimal). The default value of 1001000 appears on the prompt line (1000000 + 1000) to insure the sampling ends at the highest offset for the measurement device.

Press RETURN : The following prompt line appears: SAMPLE RESOLUTION (1-9)

The number entered represents the sampling resolution where 1 is the highest resolution (sample taken at each offset tap) and 9 is the lowest resolution (sample taken at every 9th offset tap). The default value of 1 appears on the prompt line.

Press RETURN. A prompt to probe a pin or clip a device appears.

Follow the instructions given on the screen. When the button is pressed, the status message "EXECUTING..." appears at the bottom of the screen and sampling begins (example shown in screen 5). DO NOT remove the measurement device until the entire offset range has been sampled. The status message "COMPLETE" will replace "EXECUTING...." when execution is done.

You may now use the  $\rightarrow$  and  $\leftarrow$  to move through the offset range and examine the response data at each offset tap.

#### Changing the Calibration Delay

When the calibrated offset delay for an I/O module or the probe is not appropriate for a measurement, the setoffset command may be used to change the delay. For example, if you have a signature recorded with a "-", you need to delay the calibrated offset.

The setoffset command takes an argument for the desired offset value. This offset has a bias of 1000000. So if you want to program an offset for the probe with +30 stops for sync to pod data, do the following:

sync device "/probe", mode "pod"

sync device "pod", mode "data"

status = setoffset device "/probe",

offset 1000000 + 30

The offset command returns a 1 or 0. A 1 is returned if the delay could be programmed successfully. A 0 is returned if the delay requested is outside of the range of hardware.

Delays can be varied in 4-nanosecond steps for the probe, and 15 nanosecond steps for the I/O module.

The getoffset command is valuable for accessing the current offset, such as the calibration value. To get the cal value for the probe, the command may look like this:

cal\_offset = getoffset device "/probe"

NOTE: Both the getoffset and setoffset commands reflect the values for the current sync mode only.

sexual sexue device devices readout donce dell Save car server der

#### Select:

LEARN ONE NODE FOR UFI REPEAT 1 TIMES.

Press:

info to remove the Information window.

Enter the data bus output nodes (reference designator and pin number, e.g. U14-36) from the microprocessor and the data buffers in the signal source column.

How many nodes were entered?

Place cursor on first line of the Response file if not already there.

#### Press:

F3 (LEARN) and follow instructions on display. One measurement response should be returned. The SIG response will be intensified. If this is not the case, notify the instructor.

#### Press:

Info and select:

LEARN ONE REF FOR UFI REPEAT 1 TIMES

Press Info to return to Edit Response file.

Press [53] (LEARN) then follow instructions on display.

What changed?

Place the cursor on a different reference designator and LEARN responses for it. Repeat this process until all source pins are LEARNed.

Move the cursor to the Clocked LVL column and

Press SELECT.

What happened?

Press SELECT.

Press SHIFT with SELECT.

What happened?